# University of Stuttgart Diploma Thesis

| Examiner:   | Prof. Dr. Hans-Joachim Wunderlich                               |

|-------------|-----------------------------------------------------------------|

| Supervisor: | Dr. Rainer Dorsch (hardware), Dr. Thomas Schöbel-Theuer (linux) |

|             |                                                                 |

| Begin:      | 01.05.2002                                                      |

| End:        | 31.10.2002/14.11.2002(extension)                                |

|             |                                                                 |

CR-Classification: B.7.1 C.1 C.5 D.4

Dipoma Thesis Nr. 2013

# Design of a Memory Management Unit for System-on-a-Chip Platform "LEON" Konrad Eisele

Division of Computer Architecture Institute of Computer Science Breitwiesenstr. 20-22 70565 Stuttgart A Memory Management Unit (MMU) for SoC Platform LEON was designed and integrated into LEON. The MMU comply to the SPARC Architectural Manual V8 reference MMU (SR-MMU).

# Contents

|   | 0.1        | Abbrevie  | ation inde. | <i>x</i>  |          | •••     |       |      |     | •  | <br>••• | • • | • | <br>• | <br>• | • | • | 7  |

|---|------------|-----------|-------------|-----------|----------|---------|-------|------|-----|----|---------|-----|---|-------|-------|---|---|----|

| 1 | Intro      | oduction  |             |           |          |         |       |      |     |    |         |     |   |       |       |   |   | 9  |

| 2 | Men        | nory Mai  | nagement    |           |          |         |       |      |     |    |         |     |   |       |       |   |   | 11 |

|   | 2.1        | •         | Address S   |           |          |         |       |      |     |    | <br>    |     |   |       |       |   |   | 11 |

|   | 2.2        |           | and Segme   | -         |          |         |       |      |     |    |         |     |   |       |       |   |   | 12 |

|   | 2.3        |           | re support  |           |          |         |       |      |     |    |         |     |   |       |       |   |   | 14 |

| 3 | Syste      | em-on-a-  | Chip plat   | form L    | EON      |         |       |      |     |    |         |     |   |       |       |   |   | 15 |

|   | 3.1        | LEON p    | oipeline .  |           |          |         |       |      |     | •  | <br>    |     |   |       | <br>• | • |   | 16 |

|   | 3.2        | Cache su  | ubsystem    |           |          |         |       |      |     | •  | <br>    |     |   |       | <br>• |   |   | 17 |

|   |            | 3.2.1     | Data cach   | e (DCac   | che).    |         |       |      |     |    | <br>    |     |   |       |       |   |   | 18 |

|   |            | 3.2.2     | Instruction | n cache   |          |         |       |      |     |    | <br>    |     |   |       |       |   |   | 18 |

|   |            | 3.2.3     | AMBA A      | SB inter  | face     | •••     |       |      |     | •• | <br>    |     | • | <br>• | <br>• |   | • | 20 |

| 4 | <b>SPA</b> | RC stand  | lard        |           |          |         |       |      |     |    |         |     |   |       |       |   |   | 23 |

|   | 4.1        | RISC      |             |           |          |         |       |      |     |    | <br>    |     |   |       |       |   |   | 23 |

|   | 4.2        | SPARC     | V8          |           |          |         |       |      |     |    | <br>    |     |   |       |       |   |   | 23 |

|   |            | 4.2.1     | Register w  | vindows   |          |         |       |      |     |    | <br>    |     |   |       |       |   |   | 23 |

|   |            |           | SPARC in    |           |          |         |       |      |     |    |         |     |   |       |       |   |   | 24 |

| 5 | <b>SPA</b> | RC V8 R   | eference    | MMU (     | SRMN     | MU)     |       |      |     |    |         |     |   |       |       |   |   | 27 |

|   | 5.1        | SPARC     | SRMMU       | translati | ion ove  | erview  | /     |      |     |    | <br>    |     |   |       | <br>• |   |   | 27 |

|   | 5.2        | ASI: Alt  | ternate Sp  | ace Inst  | ruction  | ns.     |       |      |     |    | <br>    |     |   |       |       |   |   | 28 |

|   |            |           | ASI:MM      |           |          |         |       |      |     |    |         |     |   |       |       |   |   | 29 |

|   |            |           | ASI:flush/  |           |          |         |       |      |     |    |         |     |   |       |       |   |   | 31 |

|   |            |           | 5.2.2.1     | flush .   |          |         |       |      |     |    | <br>    |     |   |       | <br>• |   |   | 32 |

|   |            |           | 5.2.2.2     | probe .   |          |         |       |      |     |    | <br>    |     |   |       |       |   |   | 32 |

|   |            | 5.2.3     | ASI: MM     | U diagn   | ostic a  | ccess   | I/D   | TLE  | 3.  |    | <br>    |     |   |       |       |   |   | 32 |

|   |            | 5.2.4     | ASI: MM     | U physi   | cal add  | lress r | oass  | thro | ugh | ı. | <br>    |     |   |       |       |   |   | 32 |

|   |            |           | ASI: I/DC   |           |          |         |       |      |     |    |         |     |   |       |       |   |   | 32 |

| 6 | Desi       | gn optior | ıs          |           |          |         |       |      |     |    |         |     |   |       |       |   |   | 35 |

|   | 6.1        | Physical  | ly tagged   | / physic  | cally in | dexed   | l (PT | PI)  |     |    | <br>    |     |   |       |       |   |   | 35 |

|   | 6.2        |           | ly tagged   |           |          |         |       |      |     |    |         |     |   |       |       |   |   | 35 |

|   | 6.3        | Virtually          | v tagged / virtually indexed (VTVI) (SRMMU)                                                                                   |

|---|------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------|

|   |            | 6.3.1              | Writebuffer                                                                                                                   |

|   |            |                    | 6.3.1.1 Virtual writebuffer                                                                                                   |

|   |            |                    | 6.3.1.2 Physical writebuffer                                                                                                  |

|   | 6.4        | Design of          | chosen                                                                                                                        |

|   |            | 6.4.1              | VTVI DCache, physical writebuffer (DCache.vhd)                                                                                |

|   |            |                    | VTVI ICache (ICache.vhd)                                                                                                      |

|   |            | 6.4.3              | Other changes made to LEON                                                                                                    |

| 7 | MM         | U design           | components 43                                                                                                                 |

|   | 7.1        |                    | nal overview                                                                                                                  |

|   | 7.2        |                    | ent Overview                                                                                                                  |

|   |            | -                  | Memory Management Unit (MMU)                                                                                                  |

|   |            |                    | Translation Lookaside Buffer (TLB)                                                                                            |

|   |            |                    | Translation Lookaside Buffer Entry (TLBCAM)                                                                                   |

|   |            |                    | Table Walk (TW)         51                                                                                                    |

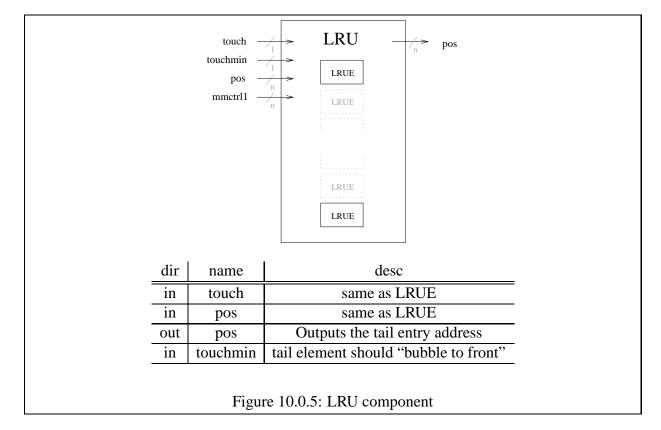

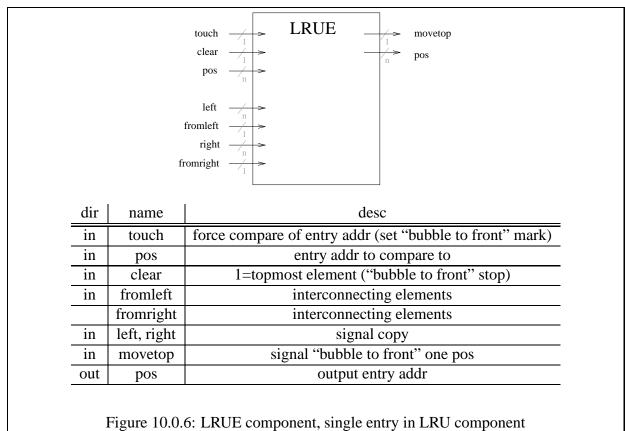

|   |            |                    | Least Recently Used (LRU & LRU entry)                                                                                         |

|   | 7.3        |                    | future optimizations                                                                                                          |

|   |            |                    | 1 cycle penalty implementation                                                                                                |

|   |            |                    | 0 cycle penalty implementation                                                                                                |

|   |            |                    | Flush optimization                                                                                                            |

| 8 | Deci       | gn Flow            | 55                                                                                                                            |

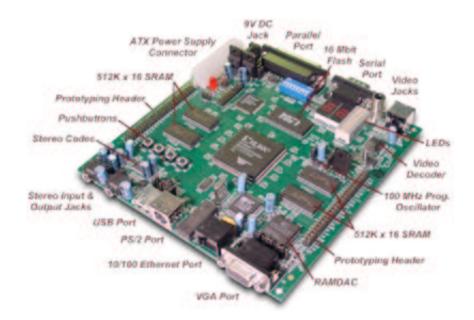

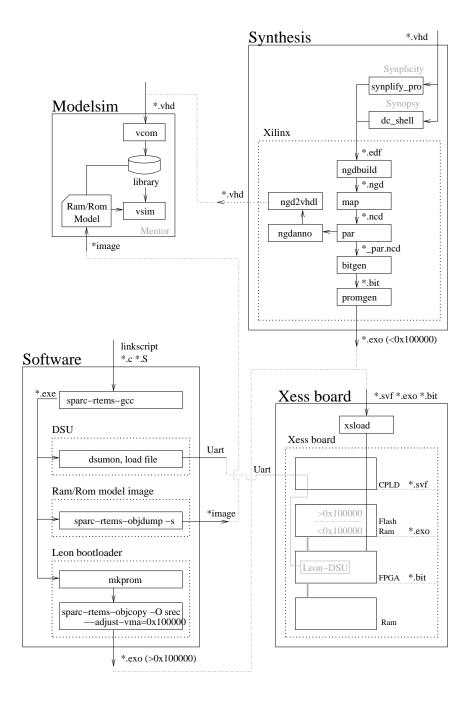

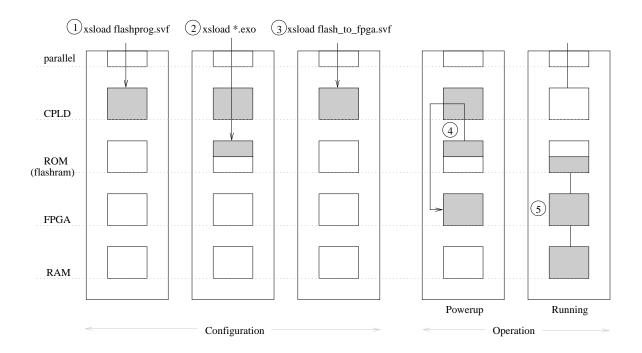

| 0 | 8.1        | 0                  | SV800 board development                                                                                                       |

|   | 0.1        |                    | Design flow                                                                                                                   |

|   |            |                    | 8.1.1.1 XESS board                                                                                                            |

|   |            |                    | 8.1.1.2 Modelsim                                                                                                              |

|   |            |                    | 8.1.1.3 Synthesis                                                                                                             |

|   |            |                    | 8.1.1.4 Software                                                                                                              |

| 9 | T in t     | ıx kernel          | 61                                                                                                                            |

| 9 | 9.1        |                    | le organization and make system                                                                                               |

|   | 9.1        |                    |                                                                                                                               |

|   |            |                    | LEON dependent parts639.1.1.1"make xconfig"63                                                                                 |

|   |            |                    | 9.1.1.2 "make vmlinux"                                                                                                        |

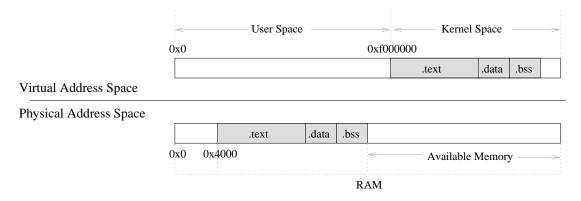

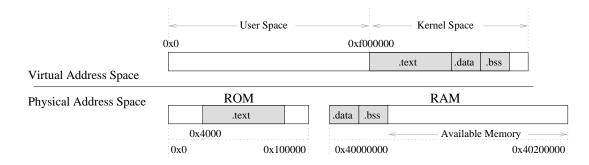

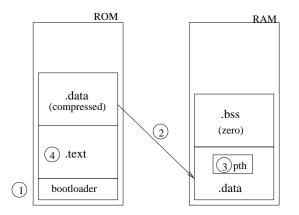

|   | 9.2        |                    | $5.1.1.2 \qquad \text{make vinimux} \qquad . \qquad $ |

|   | 9.2<br>9.3 |                    | 1                                                                                                                             |

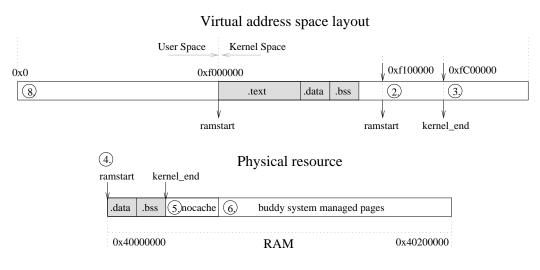

|   | 7.3        |                    | 7       65         Memory Management       66                                                                                 |

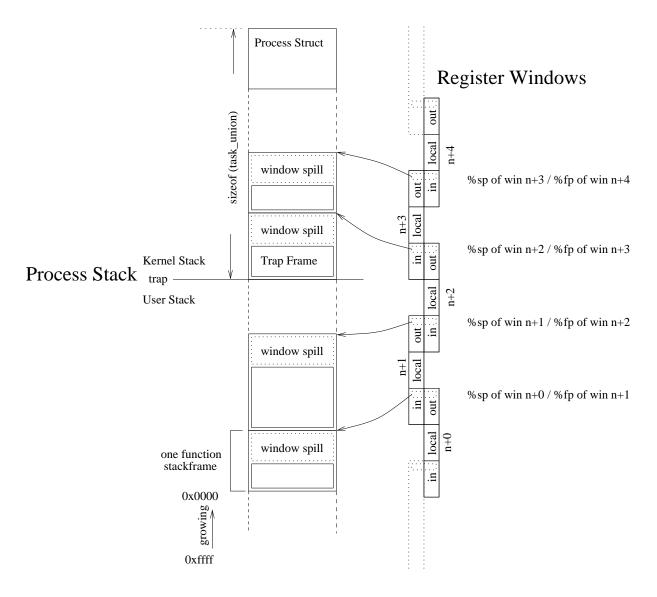

|   | 9.4        |                    |                                                                                                                               |

|   | 7.4        |                    |                                                                                                                               |

|   |            |                    |                                                                                                                               |

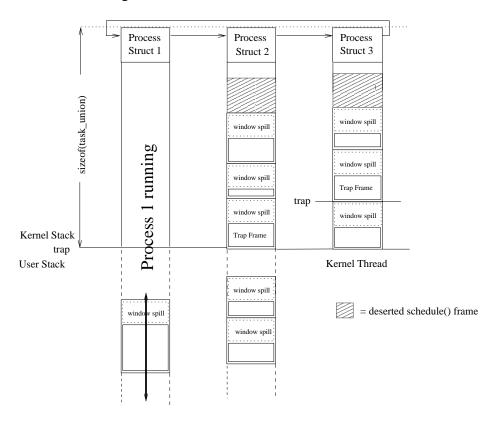

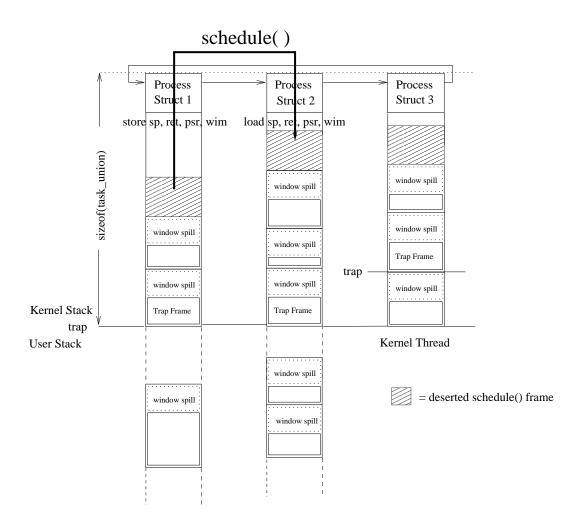

|   |            | 7. <del>4</del> .2 | Scheduling                                                                                                                    |

## Appendix A: Components

| 11  | App    | endix B: MMU distribution                             | 79 |

|-----|--------|-------------------------------------------------------|----|

|     | 11.1   | Distribution overview                                 | 79 |

|     | 11.2   | Subdirectory mmu/modelsim/                            | 79 |

|     | 11.3   | Subdirectory mmu/syn/                                 | 80 |

|     | 11.4   | Subdirectory mmu/tbench/                              | 80 |

|     |        | 11.4.1 Testbenches for MMU components mmu/tbench/comp | 80 |

|     |        | 11.4.1.1 TLB_cam.vhd                                  | 80 |

|     |        | 11.4.1.2 tw_tb.vhd                                    | 80 |

|     |        | 11.4.1.3 TLB_tb.vhd                                   | 80 |

|     |        | 11.4.1.4 mmu_tb.vhd                                   | 80 |

|     | 11.5   | Subdirectory mmu/scripts/ (XESS board development)    | 81 |

|     |        | 11.5.1 syn.pl: Xilinx tool chain build scripts        | 81 |

|     |        | 11.5.2 selexo.sh : Handling the board                 | 82 |

|     | 11.6   | Subdirectory mmu/tsource                              | 82 |

|     |        | 11.6.1 image: Creating page table hierarchies         | 83 |

|     |        | 11.6.1.0.1 Analysing page table hierarchies           | 84 |

|     |        | 11.6.1.0.2 Dumping memory content of testbench        | 85 |

|     |        | 11.6.2 Small Operating System (SOS)                   | 85 |

|     | 11.7   | Subdirectory mmu/vhdl/                                | 86 |

|     | 11.8   | Subdirectory mmu/xess/ (XESS board development)       | 86 |

| 12  | App    | endix C: MMU source                                   | 87 |

|     |        | Source code                                           | 87 |

| Bił | oliogr | aphy                                                  | 89 |

# 0.1 Abbreviation index

| AMBA   | Advance Microcontroller Bus Architecture               |

|--------|--------------------------------------------------------|

| API    | Application Programming Interface                      |

| ASB    | Advanced System Bus (AMBA)                             |

| ASI    | Alternate Space Identifiers                            |

| CAM    | Content Accessible Memory (full associative tag match) |

| CPLD   | Complex Programmable Logic Device                      |

| DCache | Data Cache                                             |

| FPGA   | Field Programmable Gate Arrays                         |

| IC     | Integrated Circuit                                     |

| ICache | Instruction Cache                                      |

| LRU    | Least Recently Used                                    |

| MMU    | Memory Management Unit                                 |

| OS     | Operating System                                       |

| PIPT   | Physically Indexed, Physically Tagged                  |

| PTE    | Page Table Entry                                       |

| PTD    | Page Table Descriptor                                  |

|        |                                                        |

7

| RTOS     | Real Time Operating System                                       |

|----------|------------------------------------------------------------------|

| SoC      | System on a Chip                                                 |

| SPARC V8 | SPARC architectural manual Volume 8                              |

| SRMMU    | SPARC Reference MMU                                              |

| TLB      | Table Lookaside Buffer (PTE cache)                               |

| VHDL     | Very High Speed Integrated Circuit Hardware Description Language |

| VIPT     | Virtually Indexed, Physically Tagged                             |

| VIVT     | Virtually Indexed, Virtually Tagged                              |

|          |                                                                  |

# Chapter 1 Introduction

This diploma thesis is inspired by the idea to get a full feature Linux API running on the open source System-on-a Chip (SoC) platform LEON, which is a synthesisable VHDL implementation of the SPARC Architectural Manual V8 standard. Linux has recently gained wide acceptance. With a rich literature footage and a broad spectrum of online documentation it is fairly well understood. Porting Linux onto LEON was especially inviting because Linux has already been ported to the SPARC architecture, running on Sun workstations<sup>1</sup>. However only SPARC processors with a Memory Management Unit (MMU) are supported. The current LEON distribution does not include a MMU because LEON is targeted on embedded realtime applications, where nondeterministic page faults of the MMU could cause trouble to the realtime requirements of these applications. Also in a deeply embedded environment, where normally only one fixed task has to run, the overhead of Virtual Memory Management is quite significant. The SPARC Architectural Manual V8 (SPARC V8) does not require a MMU to be present, however the SPARC V8 (which the LEON integer unit implements) already defines a SPARC Reference MMU (SRMMU). This suggested that when adding the SRMMU to LEON, porting Linux would be a straightforward job. Therefore, the main goal of this diploma thesis is the implementation of a SRMMU and it's integration into the LEON SoC platform. This report will concentrate on the hardware side: the design and implementation of a SRMMU. Running Linux on LEON may not be practical for embedded realtime applications, nevertheless there could be quite a few fields of application (PDA's or the like). Another nice aspect is that Linux running on LEON SoC would be Open Source from gate level on<sup>2</sup>.

The MMU supports memory management in hardware. Chapter 2 gives an introduction to the theoretical concepts of memory management. After that, chapter 3 gives a brief overview over the SoC platform LEON, which had to be extended with a MMU. The LEON integer unit implements the SPARC architecture according to the SPARC Architectural Manual V8, which is described in Chapter 4. The SPARC Architectural Manual V8 does define a reference MMU in Appendix H, the SRMMU, which is described in Chapter 5. The following chapters will focus on the implementation of the MMU in hardware. Also the SRMMU suggests a specific design in detail, there are nevertheless a variety of design options from which to choose. These options are discussed in Chapter 6. Chapter 7 describes the actual implemented design, which is the

<sup>&</sup>lt;sup>1</sup>This source turned out to be well documented and, because of the RISC nature of the low level assembler parts, relatively easy to understand

<sup>&</sup>lt;sup>2</sup>Of course excluding the tools for synthesis which are not open source (yet).

main part of this report: First a functional overview is given for the MMU as a whole, then for each operation the MMU supports. Each design component of the MMU is described separately. Some notes on future timing optimization follow. Chapter 8 will focus on the design flow, giving an overview on the tools involved. Chapter 9 start with the Linux porting effort. It will describe some fundamentals about the working of the Linux kernel and deal with aspects related to to memory management in Linux, however for detailed descriptions refer to for instance to [5]. Because of the wide range of this diploma thesis, spanning from hardware design to kernel hacking, naturally some parts will not be covered in full detail. Emphasis in this diploma thesis was put on the practical side. The source distribution can be downloaded from [7].

Development was done on a XSV300 and 800 board with a Xilinx Virtex FPGA chip for hardware prototyping.

# Chapter 2

# **Memory Management**

Historically *Memory Management* evolved out of the need implied by a multiuser/multitasking environment [14]. In such an environment, where multiple users share one memory resource, mechanisms has to be introduced to prohibit accidental access, that would crash the whole system, or unauthorized access, to protect private data. One of the first OS that pioneered the fundamental concepts of a multiuser/multitasking system was MULTICS, dating back to the late '60. It implemented the concept of virtual addresses in hardware by 2 major techniques: *paging* and *segmentation* [16]. These principles hold to date, most current architecture use paging or segmentation or a combination of both.

A Virtual Memory Management scheme is defined by two main functions: *translation* and *protection*. Translation dissolve the mapping of virtual addresses into physical addresses, which in term is closely linked to *memory allocation* - where paging is somehow related to fixed size allocation whereas segmentation is related to variable size allocation, each of which has its advantages and disadvantages. The second function is protection. Each entity in paging and segmentation hold access parameters which in turn reflect on the underlying physical resource. The SPARC Memory Management architecture, which is the target of this diploma thesis, only supports paging, therefore segmentation will only be covered briefly.

## 2.1 Virtual Address Spaces

Virtual addresses draws a clear border of abstraction. In a Virtual Memory Management scheme the actual physical memory configuration is transparent to the running program. A distinct feature of this is that programs can be programmed for an address space at compile time that is actually larger than the physical address space at runtime. The uniformity frees the programmer of memory considerations. The seamless integration of other resources than memory, such as files, reduce system and hardware dependencies [14]. Two of the main techniques for implementing virtual address spaces in hardware are paging and segmentation, which are discussed in the following sections.

## 2.2 Paging and Segmentation

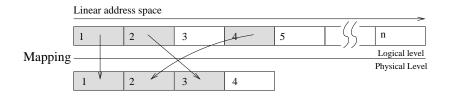

Paging use fixed size *pages* as base unit, usually 4k large. It provides one virtual address space in the logical domain, which is mapped to physical memory through one mapping entry for each page in the virtual address space, which is shown in figure 2.1. Each mapping entry holds additional information for OS use. This is shown in figure 2.1.

Figure 2.1: Paging

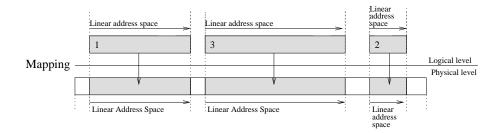

Segmentation on the other hand side uses variable size *segments*. Each segment form one independent virtual address space, however only one mapping per segment is provided, therefore a segment has to be contiguous in physical memory. Each segment holds additional information, which include its length and flags for OS use. This is shown in figure 2.2.

Figure 2.2: Segmentation

The paging example figure 2.1 shows a mapping (1,1) (2,3) (4,2). Adjacent pages in the virtual address space can be scattered in physical memory. This makes memory allocation in paging immune to fragmentation. Paging forms the base for *swapping (demand paging)* of the OS, where not the whole virtual address space has to be constantly present in physical memory. Pages can be swapped in/out from hard disc on demand. The corresponding flags in the page table entries keep track on this process.

Both paging and segmentation map from virtual addresses to physical addresses. For the translation several data structures are possible to store the mapping: It can for example be done by using one big flat table. In this case the virtual address form an offset into the table where the corresponding descriptor for the physical address is found. For the above paging example this would look somehow like this:

| virtual index | physical |

|---------------|----------|

| 1             | 1        |

| 2             | 3        |

| 3             | -        |

| 4             | 2        |

| 5             |          |

| •••           |          |

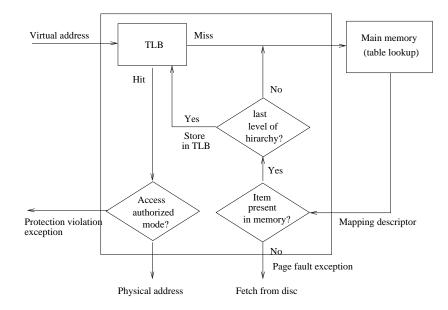

In case of segmentation a segment it is called a *segment descriptor table*. In case of paging it is called a *page table*. In case of paging with one flat page table a  $2^{**32}$  virtual address space with 4k size pages would require  $2^{**20}$  entries, which would occupy around 4 MB <sup>1</sup>[23]. Therefore in most cases a sparse *page table hierarchy* is used. An example of this can later be seen in section 5. In a page table hierarchy the virtual address is subdivided into several indices, that does each offset into the next level of the page table tree. By interrupting the traversal in between, it is also possible to define larger pages (than the fixed size 4k pages). For instance in the SPARC page table tree with 4 levels, level 0 maps 4G bytes (whole virtual address space), level 1 maps 16M, level 2 maps 256K of memory and level 3 maps the standard 4K pages. Figure 2.3 shows a schematic of the page table traversal.

Figure 2.3: Page table hierarchy traversal. (Related to [14])

Along the physical memory address the page table entries store additional flags, which enable the operating system to swap unused pages out of physical memory onto disk and implement protection on pages. In paging only *one* hardware implemented logical entity exist. Therefore protection in paging must be done by subdividing the entire virtual address space into attributed regions, merely setting another layer on top. This subdivision can only be done in the

<sup>&</sup>lt;sup>1</sup>On 64-bit computers this would even increase to  $2^{**}52$  entries which is not tolerable at all, therefore another data structure instead of a lookup table has to be used, for instance a *inverted page table*, which is a hash [23].

granularity defined by the page size (usually 4k) and is limited by the fact that these regions are bound to *one* virtual address space (overlapping may occur)[23]. The sub partitioning into different protected regions is partly done at compile time<sup>2</sup>. On the other hand side in segmentation each segment form a logical entity with its own rights<sup>3</sup>.

## 2.3 Hardware support

Hardware support include

- Table Lookaside Buffer (page table entries cache)

- Updating page table entries flags

- Exception signals

- Table walk

The most primitive form of translation would be to raise an exception on every memory access and let the OS do the translation from virtual to physical addresses in software. Hardware support accelerates this process by adding the Table Lookaside Buffer (TLB), which is in principle a cache of previous successful translations. In most cases it is build as a full-associative cache. With an appropriate processor design that tightly integrates the TLB into the overall structure the translation can be done without any delay on a TLB hit. In the course of this diploma thesis it became clear that it is hard to add a TLB with zero wait states to a design previously not designed with a MMU in mind.

On a TLB miss the page tables has to be traversed (Table walk). This can be done in hardware or in software. The advantage of a software TLB miss handle could be that an advanced TLB updating scheme could be implemented to minimize TLB misses. Nevertheless TLBs generally have a high hit ratio.

Additional hardware support is provided by updating the referenced and modified flags of a page table entry and checking access permissions. The referenced flag logs any accesses to the page, the modified flag logs write accesses to a page. These flags in turn will be used by the OS on swapping operations. On a privilege or protection violation the hardware raises a signal that cause the processor to trap.

<sup>&</sup>lt;sup>2</sup>Or dynamically using the mmap() call in Linux.

<sup>&</sup>lt;sup>3</sup>Another interesting feature of segmentation is the possibility of dynamic linking at runtime, a feature proposed by the late MINICS architecture. In a segmented Memory Management scheme a function would be a segment with the appropriate access rights. A jump to function n would equal in jumping to the offset 0 of segment n. If any program uses a distinct n at compile time relinking a new function for all running programs in the running system would be possible by exchanging the segment descriptor in the segment descriptor table at position n. No re-compilation of programs or rebooting of the whole system would necessary [23].

# **Chapter 3**

# **System-on-a-Chip platform LEON**

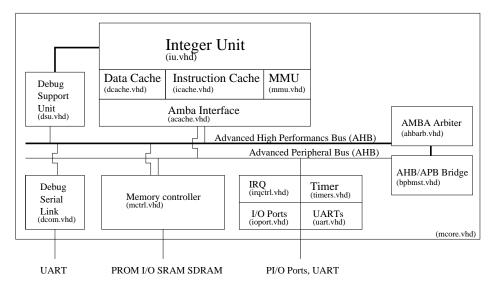

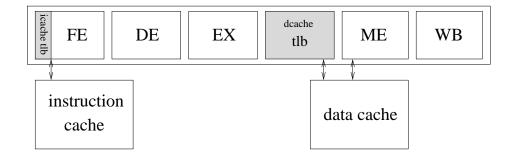

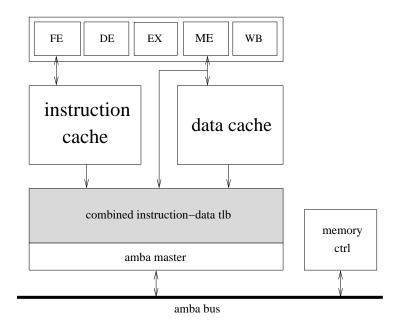

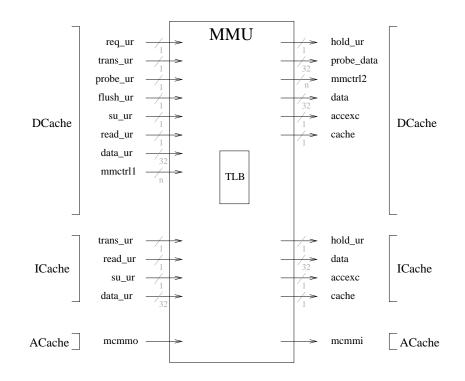

This chapter gives an overview of the LEON architecture. When adding a MMU to LEON, it had to be placed somewhere between the integer unit, the instruction cache (ICache), the data cache (DCache), and the AMBA memory interface. After giving a brief overview over the global LEON system architecture the interaction of the LEON pipeline with the DCache and ICache will be presented in more detail. Figure 3.1 shows a simplified overview of the LEON architecture.

Figure 3.1: Simplified LEON overview

The LEON source distribution is a synthesisable VHDL implementation of the SPARC Architectural Manual V8 standard. It was developed by Jiri Gaisler and can be downloaded from [8]. It is provided under the GNU Public License (GPL) [10]. It's main features are

- Integer unit

- Floating point unit

- On-chip AMBA bus (making it easy to integrate custom ip blocks into the system)

- Cache subsystem

- Hardware debug unit

- Memory controller

- UART

On the software side the following packages are available:

- RTEMS Real Time Operating System (RTOS) [3, 8], which features a Posix API. RTEMS is currently the standard application platform for programs running on LEON.

- Just recently a port of the eCos RTOS from RedHat Inc. [11] had been announced by Jiri Gaisler [8], which features a compatibility layer EL/IX that implements a POSIX API and some of the Linux APIs. <sup>1</sup>

- uCLinux OS port for LEON [17][24], which is a OS based on Linux that supports processors with no MMU.

- lecc: GNU based cross compilation system

- tsim: LEON simulator

## 3.1 LEON pipeline

The LEON integer unit (IU) implements SPARC integer instructions as defined in SPARC Architecture Manual V8. It is a new implementation, not based on previous designs. The implementation is focused on portability and low complexity, nevertheless it is very tightly woven, making it hard to integrate new features (and understand the source code). The LEON pipeline is a 5 level pipeline: fetch, decode, execute, memory and write back stage. [18]

- FE (Instruction Fetch): If the instruction cache is enabled, the instruction is fetched from the instruction cache. Otherwise, the fetch is forwarded to the memory controller. The instruction is valid at the end of this stage and is latched inside the IU.

- DE (Decode): The instruction is decoded and the operands are read. Operands may come from the register file or from internal data bypasses. CALL and Branch target addresses are generated in this stage.

- EX (Execute): ALU, logical, and shift operations are performed. For memory operations (e.g., LD) and for JMPL/RETT, the address is generated.

<sup>&</sup>lt;sup>1</sup>Real Time Operating Systems like eCos and RTEMS are aimed on a system with small memory footage and realtime requirements suitable for deeply embedded applications. For instance a simple "Hello world!" application with the RTEMS RTOS linked to it would require 133k of memory and can easily be place into ROM. Embedded applications running on a RTOS typically handle fixed tasks in signal processing or in the industrial process measurement and control environment, like finite state machines for control flow or detecting faults. The current non-MMU LEON is designed for such an realtime environment where the RTOS has to be as slim as possible.

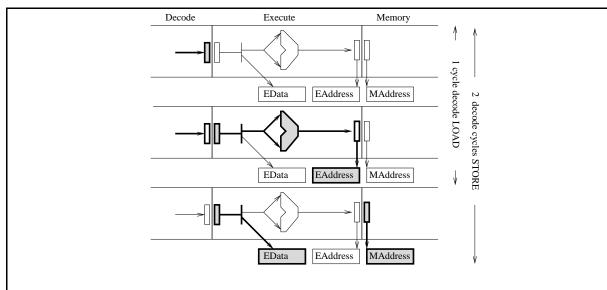

The above figure show a ld (word) and st(word) command on a DCache hit. The load command will take 1 execution cycle to process, in the execution stage the EAddress will be generated (row 2). The store command will take 2 execution stage cycles to process, in the first cycle (row 2) the EAddress is generated (that will then move into MAddress of memory stage), in the second cycle (row 3) EData (the value to store) is retrieved from the register file. The store will initialize the writebuffer, which will drive the memory request so that the pipeline can continue operation.

#### Figure 3.1.1: Load/Store commands

- ME (Memory): Data cache is accessed. For cache read hit, the data will be valid by the end of this stage, at which point it is aligned as appropriate. Store data on a cache hit read out in the E-stage (2 cycle execution stage command) is written to the data cache at this time.

- WR (Write): The result of any ALU, logical, shift, or cache read operations are written back to the register file. [18]

In principle every command takes 5 cycles to finish if no stalls occur, however the decode and execution stage are multi cycle stages that can take up to 3 cycles, for instance the store double (1dd) command would remain 3 cycles in the execution stage before pipeline continues. Memory access from data cache is initiated through the load (1d), store (st), load alternate (1da), store alternate (sta) and the atomic loadstore (1dst) and swap (swap) commands in the memory stage. Figure 3.1.1 shows a 1 cycle execution stage load (1d), and a 2 cycle execution stage store (st) command.

## 3.2 Cache subsystem

The LEON processor implements a Harvard architecture with separate instruction and data buses, connected to two independent cache controllers. Both data cache (DCache) and instruc-

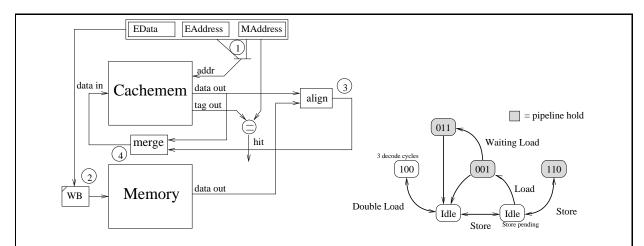

In the above figure address that drives the cachemem comes either from execution stage or from memory stage (1). Both read and write commands share a single writebuffer to issue memory requests (2) therefore read and write commands have to wait until the writebuffer empties, in which case the pipeline stalls. On a read the pipeline will of course wait for the result to be returned from memory. On a store the pipeline will stall until the writebuffer is empty. The memory result will be aligned (3) and is merged into the current cache line (4).

Figure 3.2.1: LEON DCache schematic and state transition diagram

tion cache (ICache) share one single Advanced Microcontroller Bus Architecture (AMBA) Advanced System Performance Bus (ASB) master interface to access the memory controller.

#### **3.2.1** Data cache (DCache)

The LEON DCache is a direct-mapped cache, configurable to 1 - 64 kbyte. It has a one element writebuffer that operates in parallel to the pipeline after a store operation has initialized it. The write policy for stores is write-through with no-allocate on write-miss. The data cache is divided into cache lines of 8 - 32 bytes. Each line has a cache tag associated with it, containing a tag field and one valid bit per 4-byte sub-block [18]. A simplified DCache schematic is shown in figure 3.2.1.

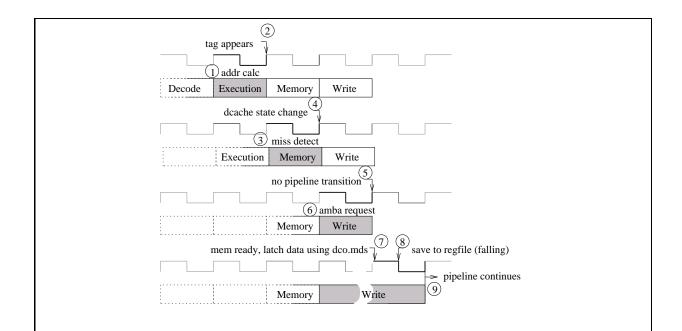

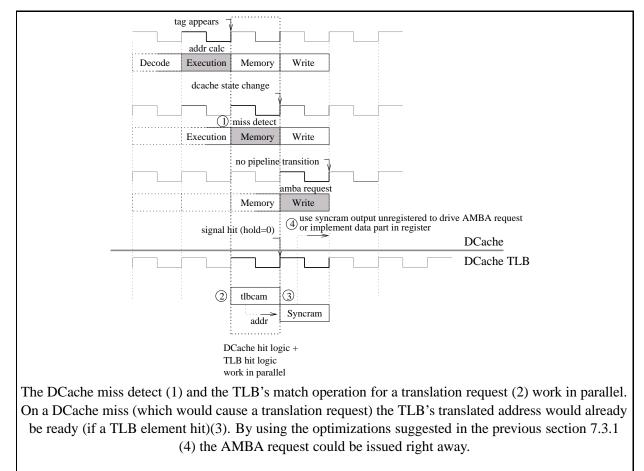

Figure 3.2.2 shows the DCache miss behavior. *This part is especially important to under*stand because the MMU's address translation will have to be done here.

#### 3.2.2 Instruction cache

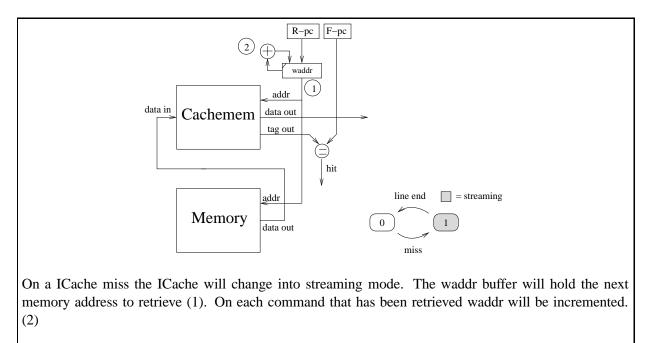

The LEON instruction cache is a direct-mapped cache, configurable to 1 - 64 kbyte. The instruction cache is divided into cache lines with 8 - 32 bytes of data. Each line has a cache tag associated with it consisting of a tag field and one valid bit for each 4-byte sub-block [18]. A simplified ICache schematic is shown in figure 3.2.3.

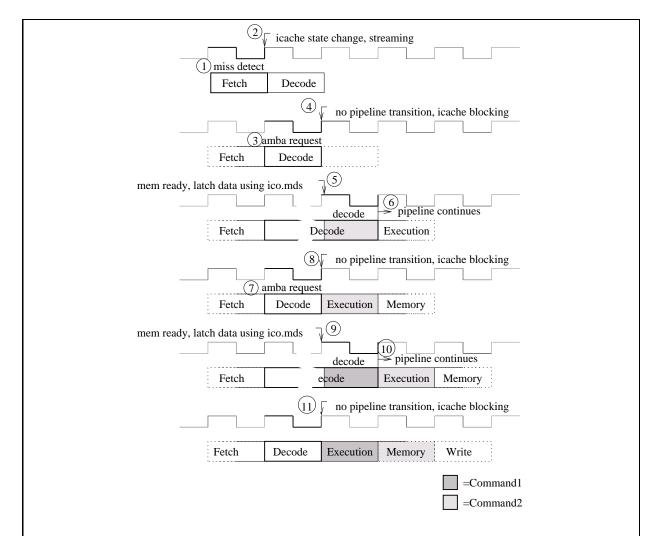

Figure 3.2.4 shows the ICache behavior on a miss. ICache will change into streaming mode, fetching one entire cache line. Because the configurable cache line size is a power of 2 and smaller than the 4k page size this operation will not cross a page boundary. Therefore only one

#### 3.2. CACHE SUBSYSTEM

The address is calculated in the execution stage (1) which will enter DCache and will be forwarded to cache's syncram to retrieve the tag. Address is either register+register or register+immediate. The tag from sycram will become valid at the beginning of the memory stage (2). In the memory stage the miss detect is made, meaning that the tag is compared with the address (3). If a miss is detected (not equal) DCache will change its state at the beginning of write stage (4) and will stall the pipeline (5) This implies that, if the following command (now in memory stage) is also a load, one wait state has to be inserted to retrieve the tag for that command after the current memory command has written its value to the cache's syncram. The memory command will therefore stall in *write stage* while the memory request is issued (6). When result is ready it is strobed into the pipeline on the dco.mds signal, bypassing the normal pipeline propagation (pipeline still stalls) (7). The result is saved to the register file on the falling edge of write stage after which the pipeline can continue (8).

Figure 3.2.2: DCache miss pipeline behaviour on a load comand

Figure 3.2.3: LEON ICache schematic

translation has to be done when changing into streaming mode.

#### 3.2.3 AMBA ASB interface

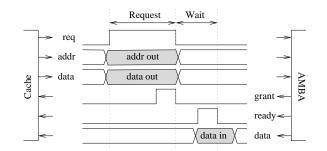

Data and instruction cache have to share one single AMBA ASB master interface. Serializing the concurrent ICache and DCache requests is done by the ACache component. A simplified ASB query is shown in the figure 3.2.

Figure 3.2: Simplified ASB query

The instruction address will either be calculated in execution stage from a previous branch or jump command or by normal increment of the pc. It is valid at the beginning of the fetch stage and will be used to retrieve the tag. The miss detect is made in fetch stage (1), if a miss was detected the ICache will change into streaming mode (2) and issue a memory request (3) while the pipeline stalls in the decode stage, waiting for a command (4). If the memory request returns, the result is strobed by the ici.mds signal into the pipeline, bypassing the normal pipeline propagation (pipeline still stalls) (5). Now the decode stage will get valid and can propagate one step at the next clock cycle (6). Meanwhile the ICache (that is still in streaming mode) issues the next memory request (7). Until it arrives the pipeline stalls again (8). (9),(10),(11) repeat this pattern.

Figure 3.2.4: ICache miss pipeline behaviour

# Chapter 4

# **SPARC** standard

The LEON integer unit implements the SPARC Architecture Manual V8 standard. This chapter tries to give a brief overview of it's RISC nature. For the details refer to [21].

## 4.1 RISC

Other than the CISC architectures, which where developed by commercial companies, the RISC architecture emerged from a research and academic surrounding [19]. The RISC key phrase was coined by the Berkeley RISC I + II project, led by David Patterson at UC Berkeley dating back to 1980. The RISC I architecture later became the foundation of Sun Microsystems's [13] SPARC V7 standard, commercialized by SPARC International Inc. [20]. Another famous RISC architecture that resembles this development is the MIPS machine, developed at Stanford led by John Hennessy, later commercialized by MIPS Technologies Inc [15].

## 4.2 SPARC V8

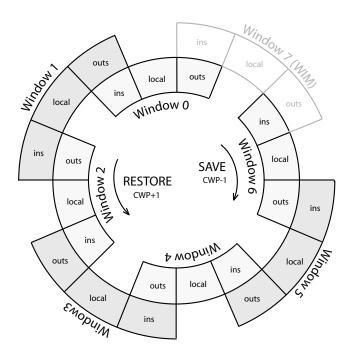

The current version 8 (V8) of the SPARC standard was first published in 1990 and can be downloaded from [21]. Like other reduced instruction set (RISC) architectures it's features include a fixed size instruction format with few addressing modes and a large register file. The distinctive feature of SPARC is it's "windowed" register file, where the instruction's source and destination register addresses are offseted by the "Current Window Pointer", this way a large pool of fast registers can be accessed, while still keeping the instruction size small.

#### 4.2.1 Register windows

Figure 4.1 illustrates the register windows for a configuration with 8 windows. The register windows are divided into 3 parts: ins, local and outs. On a SAVE instruction, which adds 1 to the Current Window Pointer (CWP), the current window's "outs" will get the new window's "ins", on a RESTORE, which subtracts 1 from the CWP, it's vice versa. On the wraparound point one invalid window exist (window 7 in the above figure). This window is marked by the Window Invalid Mask (WIM). It is invalid because it's "out" registers would overwrite the "ins"

Figure 4.1: SPARC register windows (taken from [21] p.27)

of it's neighbor which is not desirable, therefore moving into a invalid marked window will cause a trap. Typically the trap handler will take care of swapping the registers onto the stack. The "local" registers are registers that are visible only to the current function, while the "ins" and "outs" are shared between caller and callee<sup>1</sup>.

#### 4.2.2 SPARC instruction overview

All SPARC instruction are 32 bit wide. For the MMU design mainly instructions for memory access are relevant. For memory access only few "load to register" and "store from register" commands are available. The destination (for stores) and source (for loads) addressing mode is register indirect with an optional offset (either immediate or register). This enables a simple pipeline with only one memory stage. A reference to a absolute memory address will take up to 3 instructions, two instructions for initializing the address register (load lower 13 bit and load upper 19 bit) and one for the memory operation. If a base pointer is already loaded into a register (like the stack pointer) a reference will take only one instruction if a immediate offset is used, two instructions if a register has to be first loaded with the offset. Figure 4.2 gives an instruction layout overview. There are 3 main formats: Format 1 represent absolute jumps, format 2 represent the command for initializing the upper part of a 32 bit register (SETHI) and for conditional branches, format 3 represent the remaining arithmetic and control commands.

<sup>&</sup>lt;sup>1</sup>The callee has to issue a SAVE at the beginning and a RESTORE at the end when returning.

| Forma | t 1 (o | p=1): CALL       |         |         |     |     |     |          |     |     |

|-------|--------|------------------|---------|---------|-----|-----|-----|----------|-----|-----|

| op    |        |                  |         |         |     | dis | p30 |          |     |     |

| 31 30 | 29     |                  |         |         |     |     |     |          |     | 0   |

| г     |        |                  | T 0 1 1 |         |     |     |     |          |     |     |

|       | t 2 (0 | p=0): SETH<br>rd |         | nes     |     |     |     | imm22    |     |     |

| op    |        | Iu               | op2     |         |     |     |     | 11111122 |     |     |

| 31 30 | 29     | 25               | 24 22   | 21      |     |     |     |          |     | 0   |

| op    | а      | cond             | op2     |         |     |     |     | disp22   |     |     |

| 31 30 | 29     | 28 25            | 24 22   | 21      |     |     |     |          |     | 0   |

|       |        |                  |         |         |     |     |     |          |     |     |

| Forma | t 3 (0 | p=2 or 3): R     |         | instruc |     |     |     |          |     |     |

| op    |        | rd               | op3     |         | rs1 |     |     | opf      |     | rs2 |

| 31 30 | 29     | 25               | 24      | 19 18   |     | 14  | 13  |          | 5 4 | 0   |

| op    |        | rd               | op3     |         | rs1 |     | i=0 | asi      |     | rs2 |

| 31 30 | 29     | 25               | 24      | 19 18   |     | 14  | 13  | 12       | 54  | 0   |

| op    |        | rd               | op3     |         | rs1 |     | i=1 | simm     | 13  |     |

| 31 30 | 29     | 25               | 24      | 19 18   |     | 14  | 13  | 12       |     | 0   |

|       |        |                  |         |         |     |     |     |          |     |     |

Figure 4.2: SPARC instruction overview (taken from [21] p.44)

# **Chapter 5**

# **SPARC V8 Reference MMU (SRMMU)**

The MMU for LEON that is the target of this diploma thesis implements a MMU that is compliant to the SPARC Reference MMU (SRMMU): The SPARC Architecture Manual V8[21] does not require a MMU to be present, the standard rather specifies a reference MMU in Appendix H that is optional to implemented. However all commercial SPARC V8 implementation follow the SRMMU suggestion. The main features of SRMMU are:

- 32-bit virtual address

- 36-bit physical address

- Fixed 4K-byte page size

- Support for sparse address spaces with 3-level map

- Support for large linear mappings (4K, 256K, 16M, 4G bytes)

- Support for multiple contexts

- Page-level protections

- Hardware miss processing (Table Walk)

The following sections will give an overview. For more information refer to [21].

## 5.1 SPARC SRMMU translation overview

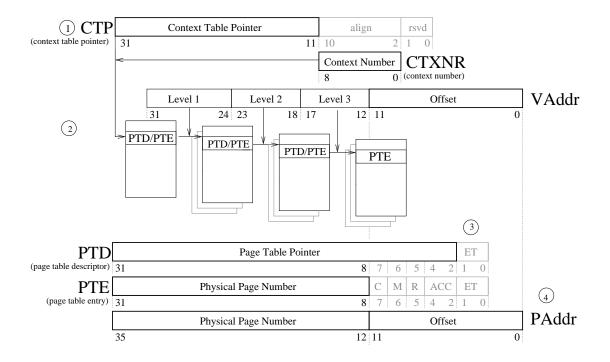

Figure 5.1 gives an detailed overview of the translation process and the data structures that are involved.

The first level of the page table hierarchy is that of the Context Table (1). It is indexed by the Context Number (CTXNR), a register that is initialized with a unique number that is associated to each process. On a process switch this register has to be updated<sup>1</sup>. The 1-4 levels of the page

<sup>&</sup>lt;sup>1</sup>The Context Number together with the virtual address form the Cache's tag, this way cache synonyms are avoided (different processes that use the same virtual address for different physical mappings). The use of the Context Number in the SRMMU suggests that the Caches should be virtually tagged / virtually indexed, which is described in Chapter 6 in more detail.

Figure 5.1: Translation overview

table hierarchy (2) are indexed through the different parts of the virtual address. If a Page Table Descriptor (PTD) is found when indexing into the Page Table, the next level is traversed, if a Page Table Entry (PTE) is found the traversal is completed. PTE and PTD are distinguished by the ET field (3), where ET=1 indicates PTD and ET=2 indicates PTE, ET=0 indicates a missing entry (page fault). Level 1 PTE (context) map to 4 GB, level 2 PTE (region) map to 16 MB, level 3 PTE (segment) map to 256k and level 4 PTE (page) map to 4k. The PTE entry includes the Physical Page Number and additional flags for protection, cache-ability and referenced/modified accounting. The physical address (4) that is the result of the translation of the MMU is formed out of the Physical Page Number and the Offset (the sizes vary depending on the page table hierarchy level).

## 5.2 ASI: Alternate Space Instructions

The privileged versions of the load/store integer instructions (ld/st), the load/store alternate instructions (lda/sta), can directly specify an arbitrary 8-bit address space identifier (ASI) for the load/store data access. The privileged alternate space load/store instructions take the form: "lda [addr] asi\_ident,%r" and "sta %r,[addr] asi\_ident", where asi\_ident is the 8 bit ASI identifier. The address and the value (in case of a store) are interpreted in a specific way that differ for each ASI identifier<sup>2</sup>. The privileged load/store alternate instructions can be used by supervisor software to access special protected registers, such as MMU, cache control, and

<sup>&</sup>lt;sup>2</sup>For instance for ASI identifiers "DCache\_flush" on a store to *any* address DCache is flushed. In other ASI identifier spaces addresses are mapped to special registers, that can be stored or loaded just like normal memory.

processor state registers, and other processor or system dependent values [21]. For the MMU the SPARC Architecture Manual V8 suggests the ASI "MMU register" (0x4), ASI "MMU flush/probe" (0x3), ASI "MMU bypass" and a optional ASI "MMU diagnostic access I/D TLB" (0x7). For fine grade cache flushing (flushing depending on ctx number and a virtual address pattern) five additional "I/DCache flush" ASIs are suggested.

#### 5.2.1 ASI:MMU register access

Alternate space "MMU register" gives access to the MMU's control registers. The instructions "lda [addr] asi\_mmureg, %r" and "sta %r,[addr] asi\_mmureg" behave as you would expect. For detailed information refer to [21] Appendix H. There are 5 registers defined for the SRMMU:

| [addr] | register                |

|--------|-------------------------|

| 0x0xx  | Control Register        |

| 0x1xx  | Context Table Pointer   |

| 0x2xx  | Context Number Register |

| 0x3xx  | Fault Status Register   |

| 0x4xx  | Fault Address Register  |

• **Control Register**: This register include enable flag and implementation specific flags among others.

|    | IMPL | Ver   | Custom |   | PSO | resvd | NF | Е | ] |

|----|------|-------|--------|---|-----|-------|----|---|---|

| 31 | 1 28 | 27 24 | 23     | 8 | 7   | 6 2   | 1  | 0 |   |

- IMPL: MMU Implementation.

- VER: MMU Version .

- SC: System control.

- PSO: Partial Store Order.

- NF No Fault bit, disable fault=1 trap.

- E Enable, enable = 1.

- Context Pointer register: This register holds the root of the page table tree.

• **Context Number register**: This register stores the context number of the running process. It will form the offset into the context table.

• **Fault status register**: This register holds the status of the MMU on a exception (i.e. page fault).

| reserved |    | EBE |    |   | L |   | AT | FT |   | F | AV | OW |

|----------|----|-----|----|---|---|---|----|----|---|---|----|----|

| 31       | 18 | 17  | 10 | 9 | 8 | 7 | 5  | 4  | 2 |   | 1  | 0  |

- EBE: unused

- L: The Level field is set to the page table level of the entry which caused the fault:

| L | Level                  |

|---|------------------------|

| 0 | Entry in Context Table |

| 1 | Entry in Level-1 Page  |

| 2 | Entry in Level-2 Page  |

| 3 | Entry in Level-3 Page  |

- AT: The Access Type field defines the type of access which caused the fault:

| AT | Access Type                                    |

|----|------------------------------------------------|

| 0  | Load from User Data Space                      |

| 1  | Load from Supervisor Data Space                |

| 2  | Load/Execute from User Instruction Space       |

| 3  | Load/Execute from Supervisor Instruction Space |

| 4  | Store to User Data Space                       |

| 5  | Store to Supervisor Data Space                 |

| 6  | Store to User Instruction Space                |

| 7  | Store to Supervisor Instruction Space          |

- **FT:** The Fault Type field defines the type of the current fault:

| FT | Fault type                |  |  |  |  |  |  |  |  |

|----|---------------------------|--|--|--|--|--|--|--|--|

| 0  | None                      |  |  |  |  |  |  |  |  |

| 1  | Invalid address error     |  |  |  |  |  |  |  |  |

| 2  | Protection error          |  |  |  |  |  |  |  |  |

| 3  | Privilege violation error |  |  |  |  |  |  |  |  |

| 4  | Translation error         |  |  |  |  |  |  |  |  |

| 5  | Access bus error          |  |  |  |  |  |  |  |  |

| 6  | Internal error            |  |  |  |  |  |  |  |  |

| 7  | Reserved                  |  |  |  |  |  |  |  |  |

• Fault address register: This register holds the virtual address that caused the exception:

|    | virtual address |

|----|-----------------|

| 31 | 0               |

#### 5.2.2 ASI:flush/probe

Alternate space "flush/probe" gives access to the MMU's translation process and the TLB. A *read* access to ASI "flush/probe" will initiate a probe operation, either returning the PTE or  $zero^3$  - a *write* access will initiate a flush operation, that will remove entries form the TLB. The flush/probe criteria is coded into the write/read address and has different meanings for flush and probe. It has the following format:

| Virtual Flush Probe Address | 1     | ype | reserved |   |

|-----------------------------|-------|-----|----------|---|

| 31                          | 12 11 | 8   | 7        | 0 |

- Virtual Flush/probe address: The index part of the virtual address.

- Type:

| Туре         | Probe                     | Flush                             |  |  |  |  |  |

|--------------|---------------------------|-----------------------------------|--|--|--|--|--|

| 0 (page)     | probe until Level-3 entry | flush Level-3 PTE                 |  |  |  |  |  |

| 1 (segment)  | probe until Level-2 entry | flush Level-2 & 3 PTE/PTDs        |  |  |  |  |  |

| 2 (region)   | probe until Level-1 entry | flush Level-1, 2 & 3 PTE/PTDs     |  |  |  |  |  |

| 3 (context)  | probe until Level-0 entry | flush Level-0, 1, 2, & 3 PTE/PTDs |  |  |  |  |  |

| 4 (entire)   | probe until Level-n entry | flush all PTEs/PTDs               |  |  |  |  |  |

| 5 - 0xF none |                           |                                   |  |  |  |  |  |

<sup>&</sup>lt;sup>3</sup>Probe operation will return the PTE of the page table hierarchy, not the physical address the is coded into the PTE. The probe operation can also be done in software, using the ASI "MMU physical address pass through" and traversing the page table hierarchy by hand. In fact the probe operation is rarely used.

#### 5.2.2.1 flush

A flush operation takes the form "sta %r, [addr] asi\_flush\_probe", where data supplied in %r is ignored and addr forms the flush criteria (see above). Entries from the TLB satisfy the given criteria are flushed. For detailed information refer to [21] Appendix H, p. 250.

#### 5.2.2.2 probe

A probe operation takes the form "lda [addr] asi\_flush\_probe,%r", where addr forms the probe criteria (see above). The return value is either the PTE or zero. For detailed information refer to [21] Appendix H, p. 250.

|            | Level 0   |   |   | Level 1       |         |   | Level 2 |    |   |         | Level 3 |    |   |   |   |   |  |

|------------|-----------|---|---|---------------|---------|---|---------|----|---|---------|---------|----|---|---|---|---|--|

| probe Type | 2         | 3 | 0 | 1             | 2       | 3 | 0       | 1  | 2 | 3       | 0       | 1  | 2 | 3 | 0 | 1 |  |

| 0(page)    | 0         | 0 | 0 | =>            | 0       | 0 | 0       | => | 0 | 0       | 0       | => | * | 0 | * | 0 |  |

| 1(segment) | 0         | 0 | 0 | $\Rightarrow$ | 0       | 0 | 0       | => | * | * 0 * * |         |    | - |   |   |   |  |

| 2(region)  | 0         | 0 | 0 | =>            | * 0 * * |   | -       |    |   |         | -       |    |   |   |   |   |  |

| 3(context) | *         | 0 | * | *             | -       |   |         | -  |   |         |         | -  |   |   |   |   |  |

| 4(entire)  | *         | 0 | 0 | =>            | *       | 0 | 0       | => | * | 0       | 0       | => | * | 0 | 0 | 0 |  |

| 5-0xf      | undefined |   |   |               |         |   |         |    |   |         |         |    |   |   |   |   |  |

\*=value, 0=zero, "=>"= follow [21]

#### 5.2.3 ASI: MMU diagnostic access I/D TLB

Alternate space "MMU diagnostic access I/D TLB" gives direct read/write access to the TLB. This ASI is not intended for system operation but for system debugging only. It is not required to be implemented. The SRMMU specification gives a suggestion of the coding of the address/data supplied by the "lda [addr] asi\_iodiag, %r" and "sta %r,[addr] asi\_iodiag" command, however these are highly implementation specific. The method implemented in this diploma thesis simply reads out the whole TLB entries content to ram using the AMBA interface already connecting the TLB for write-back of page table entries who's referenced or modified bits has changed. This ASI can be removed when system has proven to works properly. Write operation on TLB is not supported.

## 5.2.4 ASI: MMU physical address pass through

Alternate Load/Store with the ASI "MMU physical address pass through" bypass the MMU translation, i.e. this can used to modify the page table hierarchy on bootup. The original SPARC suggestion for this ASI is 0x20-0x2f. For detailed information refer to [21] Appendix I, p. 267.

## 5.2.5 ASI: I/DCache flush

This ASI affects the cache itself (not the TLB). This ASI is used by Linux and is thus added to the DCache controller's ASI decoder. A alternate Store with the Alternate Space Identifier

"I/DCache flush" will flush I/DCache entries given a specific criteria. For detailed information refer to [21] Appendix I, p. 266. In the current implementation any alternate store to ASI "I/DCache flush" *will flush the whole I/DCache*, a future enhancement could be the implementation of a fine grade flush that is suggested by the SPARC standard.

# Chapter 6

# **Design options**

There are several possibilities for implementing a MMU for LEON, each of which would have to be integrated into a different place of the current design. For the cache/MMU integration any of the three alternatives, "physically tagged and physically indexed" (PTPI), "virtually tagged and physically indexed" (VTVI) has its drawbacks and advantages that are discussed in the following chapter. The SRMMU actually suggests to use a the VTVI design by introducing the Context Number register, however also a PTPI or VTPI design could be implemented that complies to the SRMMU standard.

In a VTVI design there are again 2 choices to choose from: virtual writebuffer (translation *after* initialization of writebuffer) or physical writebuffer (translation *before* initialization of writebuffer). The VTVI design with a physical writebuffer and a combined I/DCache TLB is the most simple design to implement.

## 6.1 Physically tagged / physically indexed (PTPI)

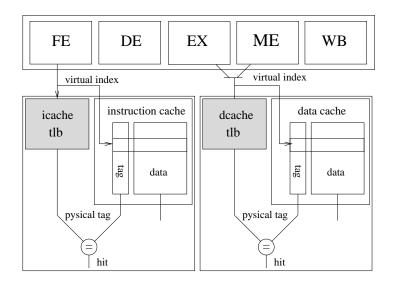

On a PTPI design one TLB lookup has to be made on every cache access. This requires the TLB lookup to be integrated into the pipeline to get reasonable performance. In a PTPI design shared pages among different processes are possible (with any virtual address mapping), which means sharing of cache line among different tasks is possible. Cache *snooping* is possible<sup>1</sup>. A PTPI integration is shown in figure 6.1.

Implementing such a scheme into LEON would be difficult because it would mean in fact to rewrite the pipeline. An advantage would be that DCache and ICache could be left unchanged, with snooping enabled.

## 6.2 Physically tagged / virtually indexed (PTVI)

The PTVI design combines the physical with the virtual cache design: The drawback of a pure physical cache is that the TLB lookup has to be done before every cache access, the drawback of s pure virtual cache design is that context information has to be added to avoid the synonym

<sup>&</sup>lt;sup>1</sup>In Cache Snooping the AMBA Bus is constantly checked to see weather another AMBA Bus Master is modifying a memory location which is stored in the Cache

Figure 6.1: Pipeline with physically tagged and physically indexed cache

problem (see section 6.3). The PTVI design still has to do a TLB lookup on every cache access, but because the cache index is virtual the tag retrieval can be initiated right away while the TLB lookup is done in parallel. Because the tag is physical no synonyms can occur, therefore no context information is needed. This also means that sharing cache line among different processes is possible (yet the virtual addresses mappings have to be equal<sup>2</sup>). Cache *snooping* is not possible. Therefore on a memory access by another AMBA master Cache integrity has to be maintained my software. A PTVI integration is shown in figure 6.2.

Figure 6.2: Pipeline with virtually tagged and physically indexed cache

Because the TLB lookup has to be done in one cycle (until the tag arrives) either a dual port syncram or a split instruction/data cache has to be implemented so that instruction/data cache can work in parallel. Integration could be done in ICache and DCache with minor changes in the cache - pipeline inter-working.

<sup>&</sup>lt;sup>2</sup>Cache lines that store the Linux kernel could be shared by all processes , because the kernel is compiled to a fixed vaddress.

## 6.3 Virtually tagged / virtually indexed (VTVI) (SRMMU)

The main advantage of a VTVI design is that the TLB lookup is positioned *after* the cache. This leaves the pipeline - cache inter-working unchanged. Only on a a cache miss the TLB lookup is initiated. Because two virtual addresses can point to the same physical address (*synonym*) the cache tag has to be extended with the *context number* so that each address of different virtual address spaces of different processes are distinct. This leads to multiple cache lines if the same physical address is referenced by multiple contexts, which is a drawback. Cache *snooping* is not possible. A VTVI integration is shown in figure 6.3.

Figure 6.3: Pipeline with virtually tagged and virtually indexed cache

The VTVI design is proposed by the SRMMU. It is the easiest design to implement because it is fairly sequential.

## 6.3.1 Writebuffer

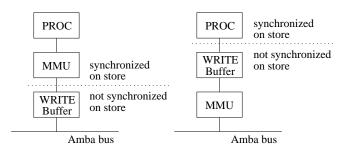

In LEON on a store command the writebuffer (if empty) will be initialized and will work in parallel to the pipeline. When using a VIVT cache the writebuffer can be initialized by virtual addresses, in which case the address translation is done *after* initializing the writebuffer, or as a physical writebuffer, in which case the translation is done *before* initializing the writebuffer. The difference of a physical and a virtual writebuffer is shown in figure 6.4.

### 6.3.1.1 Virtual writebuffer

A virtual writebuffer implies that on a MMU exception the pipeline state can *not* be recovered because a exception will take place after the pipeline has already continued for some time (the exception is deferred). Without extra precautions this leads to some situations where a *trap in*

Figure 6.4: left: physical writebuffer. right: virtual writebuffer

*trap* would occur, which is prohibited in SPARC and would force the processor in error mode. One example (which does not occur in LEON because the writebuffer in LEON is only a one element writebuffer) would be if 2 succeeding memory writes that both cause an exception would be stored in the writebuffer. In this case the second store could not be emptied after the first exception caused a trap. Another example (that could occur on LEON and that would need to require to add extra logic) would occur when ICache and DCache would both cause a trap at the same time : (Jiri Gaisler pointed to this problem)

st %11,[%12]

add 0x1,%10

If st would trap in DCache (memory stage) and add would trap in ICache (fetch stage, i.e. page fault), the add trap could bypass the st trap in the pipeline because the st trap could be deferred by the writebuffer. This again would cause a trap in trap situation (the writebuffer, this time a one element writebuffer, could not be emptied). This situation can only be avoided if, on a trap in ICache, the writebuffer in DCache is forced to be emptied first, before the pipeline can continue, initiate a possible trap before the ICache trap could be initiated.

### 6.3.1.2 Physical writebuffer

A physical writebuffer runs in sync with the pipeline and therefore the trap in trap problem does not occur. However a address translation has to be made before the writebuffer can be initialized, therefore part of it's parallelism to the pipeline is lost.

# 6.4 Design chosen

In this chapter 2 alternatives are presented: the *virtual* and the *physical* writebuffer design. Both designs where implemented, however in the end the physical writebuffer was chosen, because this way the pipeline can be left unchanged.

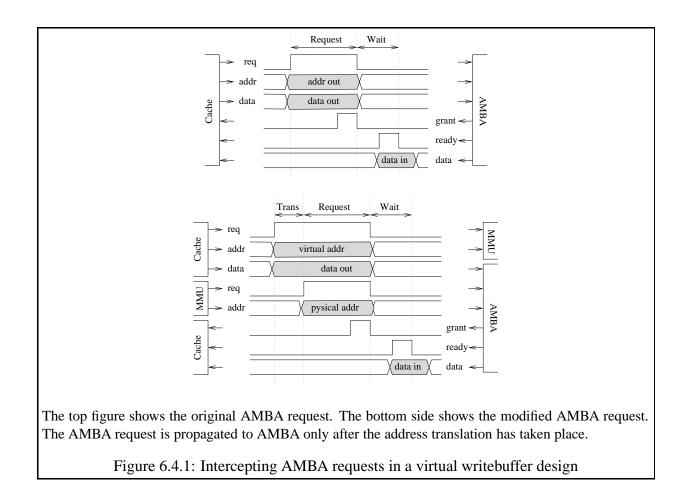

In the first design a VTVI cache design with a *virtual* writebuffer was implemented. This enabled to program the MMU as a plug and play component, leaving the DCache unchanged (except for the added context information). All the MMU had to do was to intercept the AMBA requests, forwarding them only after the translation had finished. Also it has been changed, this design is shown for completeness in figure 6.4.1.

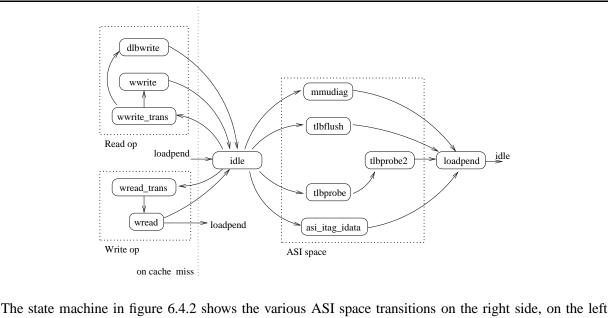

side the read and write operations perform a translation in state "wread\_trans" and "wwrite\_trans" before initializing the writebuffer. State "wread" will wait for the result to be returned (stalling the pipeline), if a memory access command follows immediate after the current command, the loadpend state is inserted. State "write" will initialize the writebuffer with the translated address and will return immediately.

Figure 6.4.2: New DCache state machine

The *virtual* writebuffer design gave rise to the *trap in trap* problem. This could be fixed with changes in the pipeline, however instead in the second run the VTVI cache design with a *physical* writebuffer was chosen. In this case the DCache and ICache had to be reprogrammed.

### 6.4.1 VTVI DCache, physical writebuffer (DCache.vhd)

The DCache has been rewritten. It now implements a VTVI cache with a physical writebuffer, context information was added to the tag field. The ASI spaces decoder was extended to support "flush/probe", "MMU register", "MMU bypass", "I/D flush" and and "Diagnostic access" accesses. A DCache state diagram is shown in figure 6.4.2.

## 6.4.2 VTVI ICache (ICache.vhd)

The data cache has been rewritten. It now implements a VTVI cache, context information was added to the tag field. The address translation is done before entering the ICache's streaming mode. A ICache state diagram is shown in figure 6.5.

### 6.4.3 Other changes made to LEON

• AMBA interface (acache.vhd)

The AMBA master interface was rewritten and arbiters between ICache, DCache and the

Figure 6.5: New ICache state machine

table walk component. ICache component has highest priority.

- Cachemem (cachemem.vhd) Context number information was added to every i/DCache line.

- SPARCv8.vhd: has been changed by adding the new ASI space identifiers. Because the ASI space identifiers proposed by [21] in Appendix I are already used by LEON, another partitioning was used.

- iu.vhd: the pipeline was slightly changed to propagate the supervisor mode flag to the execution stage.

# Chapter 7

# **MMU design components**

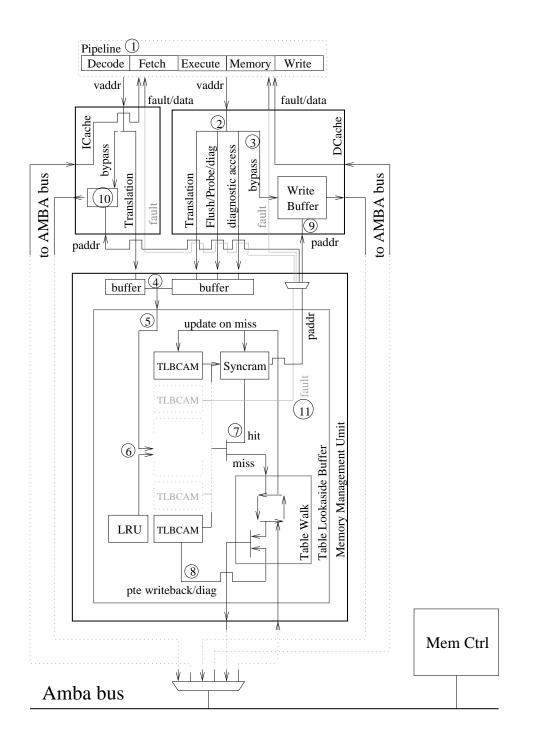

Figure 7.1: MMU schematic

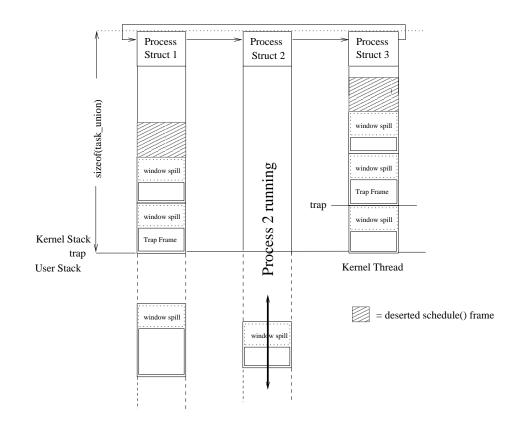

Figure 7.1 gives an overview of the MMU as a whole. It's individual components (MMU, TLB, TLBCAM, Table Walk, LRU) will be described in the next chapter in more detail. The figure tries to visualize the data paths in a simplified way: ICache and DCache receive virtual addresses for translation (1), in addition DCache will also handle the various ASI identifiers for the MMU. "MMU Flush/Probe" and "MMU I/D diagnostic access" will be forwarded to the MMU (2), the other ASI identifiers are handled inside DCache. The translation operation can be bypassed in case the MMU is disabled or if ASI "MMU physical address pass through" is used. In this case the writebuffer of DCache and the instruction address buffer in ICache (3) will be initialized immediately and an AMBA request will be issued. In case of MMU is enabled a translation will be requested from ICache and DCache. If a ICache and DCache request is issued at the same time they are serialized, the request that has to wait will be buffered in the meantime (4). ICache's translation request and DCache's translation, flush/probe and "diagnostic access" requests will then be issued serially to the Table Lookaside Buffer (TLB) (5). The translation operation, flush operation and probe operation will be described in the following section ("Functional overview"). The "diagnostic access" operation is already been described in section 5.2.3. The translation, flush and probe operation will initiate different match operations on the TLBCAM (6) that will assert a hit on success (7). In case of translation operation and probe operation a miss will initiate a Table Walk that will traverse the Page Table Hierarchy. After the Page Table Entry is retrieved from memory the new entry will be stored in TLBCAM (tag) and syncram (data). The TLBCAM entry that is going to be replaced (which is determined by the LRU component) will be checked for memory synchronization (ref/modified bit changed) (8). After completion the result is returned to the MMU from the TLB: a translation operation will return the physical address that is used in DCache to initialize the Writebuffer (9) and in ICache to initialize the instruction address buffer (10), that is used for increment in streaming. A probe operation will return the probed Page Table Entry. A translation operation will also check for permissions, on a protection or privilege violation a exception is raised (11). DCache/ICache and Table Walk AMBA requests are handled using one single AMBA bus master interface (12).

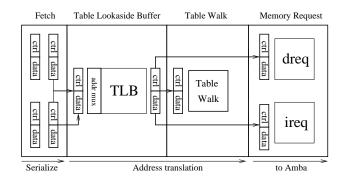

Another alternative view is given in figure 7.2 that visualizes the translation process as a pipeline, with 4 stages, "Fetch", "Table Lookaside Buffer", "Table Walk" and "Memory Request". This figure is only for making the translation concept explicit. <sup>1</sup>

## 7.1 Functional overview

The three main MMU operations are: translation, flush and probe. Each of these operations is described:

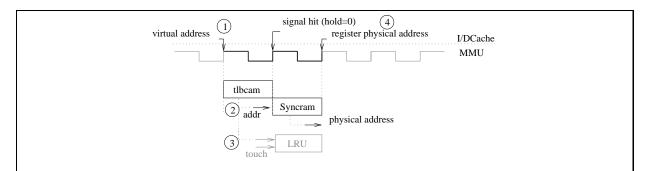

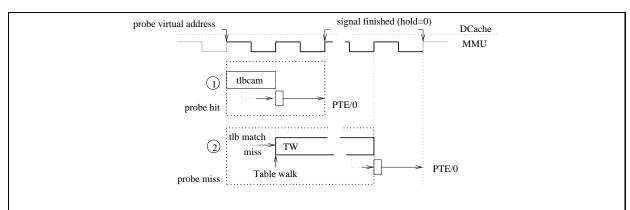

• Translation operation on a TLB hit is shown in figure 7.1.1.

<sup>&</sup>lt;sup>1</sup>In the pipeline schematic figure a zero wait state translation would be realized by feeding in translation addresses while cache hit check is made. The pipeline propagation from "Table Lookaside Buffer" to "Table Walk" (in case of a miss) or "Memory Request" (in case of a hit) would be blocked if the cache asserted hit (no translation needed). Either DCache or ICache translation request would be allowed to perform such a pre-translation.

In case of a physical writebuffer the writebuffer is in sync with the pipeline. Therefore ICache and DCache will only issue one translation request at a time. In case of a virtual writebuffer, where the writebuffer is not in sync with the integer unit pipeline (translation can be deferred) multiple DCache translation requests can be waiting in a queue. Therefore a MMU *pipeline* would make sense only for a virtual writebuffer design.

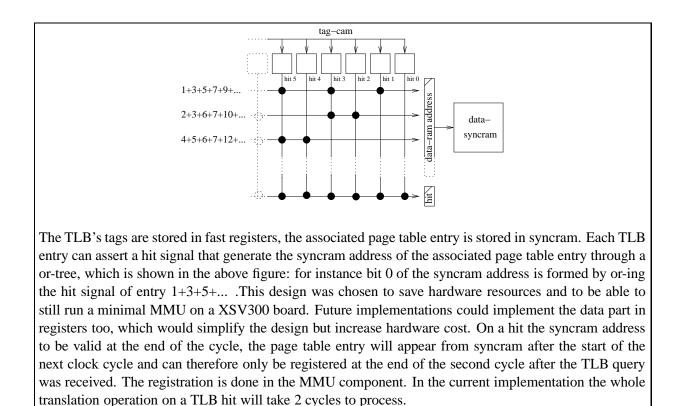

Figure 7.2: Pipeline view

At rising edge the virtual address enters TLB (1). It is matched concurrently by all TLB entries. Each can generate a hit signal, only one element per match operation is expected to raise the hit signal, that is used to form the syncram address (2), if multiple hit signals are raised the result is unspecified. The entry that signalled a hit will be marked in the Least Recently Used (LRU) component (3). If a hit has occurred the hold signal will be deasserted, physical address of the translation will be valid at the end of the following cycle and will be registered (4). The following is not shown in the above figure: The permission flags are checked against the information given by I/DCache: supervisor access, ICache or DCache access and read or write access. On a protection or privilege violation the fault signal is raised. Also the referenced/modified bits of the hit entry is updated. It will not be synchronized with memory until the entry is flushed or replaced.

Figure 7.1.1: TLB on a hit

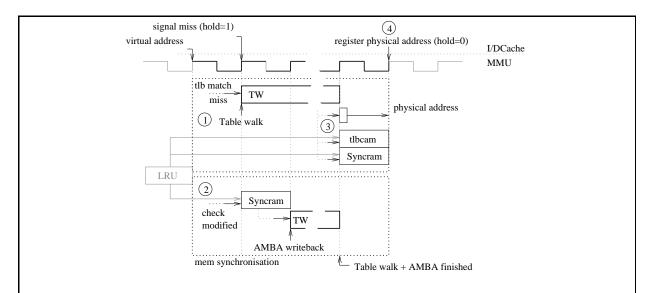

- Translation operation on a TLB miss is shown in figure 7.1.2.

- The TLBCAM address generation is shown in figure 7.1.3.

- Probe operation on a TLB hit/miss is shown in figure 7.1.4.

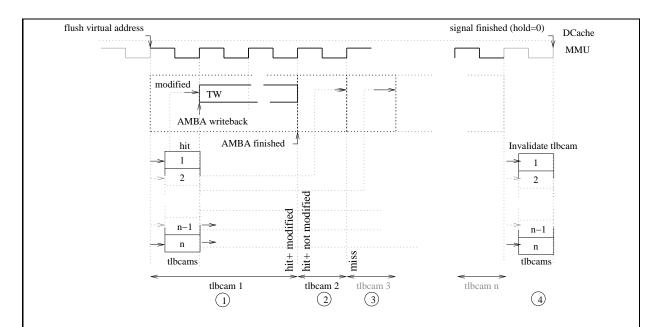

- Flush operation is shown in figure 7.1.5.

On a TLB miss the Table Walk (TW) is initialized (1). Both the table walk in the TW component and the AMBA writeback operation of the TLB component use one single interface to the AMBA interface of the AMBA master (acache.vhd). The next update position is determined by the Least Recently Used (LRU) component. If the referenced/modified bit of the PTE of the TLB entry that is going to be replaced has to be synchronized with memory the PTE will be retrieved from syncram and will be updated in memory through the AMBA interface (2). When the Table Walk finishes the retrieved PTE is stored in syncram and the corresponding TLB entry is initialized (3). After another cycle the translated physical address is valid (4). The following is not shown in the above figure: In addition the PTE's physical memory address is stored so that on a writeback operation (when synchronizing the PTE's ref/modified flag) the Page Table Hierarchy has not to be traversed. Access permissions are checked.

Figure 7.1.2: TLB on a miss

#### Figure 7.1.3: TLB hit logic

The probe operation is initiated through a read access with ASI identifier "MMU flush/probe". A probe operation will retrieve a PTE from a given virtual address pattern. On a probe operation first the TLBCAM probe match operation is done (1) (which is different to the translation match operation). If a hit occurs either PTE or zero is returned. If no hit occurred the Table Walk is initiated (2) and either a PTE entry or zero is returned. (see Section 5.2.2 for detailed description).

Figure 7.1.4: Probe operation with TLB hit/miss

The flush operation is initiated through a write access with ASI identifier "MMU flush/probe". The flush operation in the current implementation will take at least one clock cycle per TLB entry, to perform a flush match operation (which is different to translation match and probe match operation). If memory synchronization is needed additional cycles for the AMBA request are needed. At the end one cycle is needed to invalidate the matched TLB entries of the flush operation. TLB entries are checked one by one, First a hit against the virtual flush address (Section 5.2.2) is generated. In case of a hit *and* if the referenced/modified flags have been changed, the entry is written back to memory. This is shown in the above figure, where 3 examples are shown: (1) TLBCAM 1 signals a hit and that it needs synchronization, and therefore a AMBA writeback operation is started. (2) TLBCAM 2 signals a hit but does not need synchronization and therefore AMBA writeback operation is not started. (3) TLBCAM 3 has not hit at all. At the last cycle all entries that have hit are invalidated. In the example this would be entry 1 and 2, entry 3 would be left valid (4).

Figure 7.1.5: Flush operation

## 7.2 Component Overview

## 7.2.1 Memory Management Unit (MMU)

The MMU component is shown in figure 10.1 and table 10.1. The main purposes of the MMU component are:

- Serialize the concurrently arriving translation requests from ICache and DCache.

- Implement fault status and fault address register (ASI space "MMU register")

DCache and ICache have to share a single TLB resource therefore stalls can occur. DCache misses result in one TLB query for Load/Store operations. Double word accesses are double word aligned. Therefore they will not cross a page boundary and only one translation is needed. ICache cache misses result in one TLB query, however in streaming mode the translated physical address is used for increment. therefore for a 4 word size ICache line only one in four instruction results in a TLB query. Requesting a TLB operation for DCache is done by asserting req\_ur. This can be a translation(trans\_ur), a flush (flush\_ur) or a probe (probe\_ur) operation. Requesting a TLB translation for ICache is done by asserting trans\_ur. The various parameters for these operations are registered inside the MMU so that concurrent request from ICache and DCache can be serialized. Until the operation result to DCache or ICache is returned hold\_ur will remain asserted.

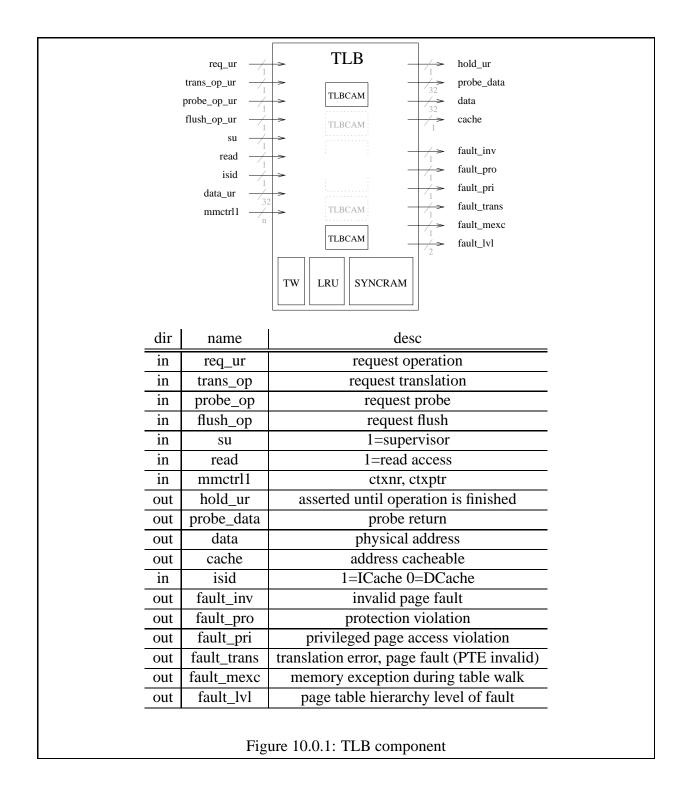

### 7.2.2 Translation Lookaside Buffer (TLB)

The TLB component is shown in figure 10.0.1.

Being a cache of previous translations, the TLB can be designed in similar ways as the data/instruction caches: direct mapped, n-way associative or full associative. Most TLBs however are full associative to maximize speed (implemented as registers) and to minimize the miss rate by choosing a appropriate replacement scheme. In VIPT or PIPT cache designs TLB dualport tag-cam or split instruction/data TLBs are required to get reasonable speed. Because LEON has to run on resource poor hardware, the VIVT cache solution was best suited that allows a mixed Tag-Cam/Data-Ram on a combined Instruction/Data cache TLB. TLB receive the already serialized ICache and DCache requests from MMU.

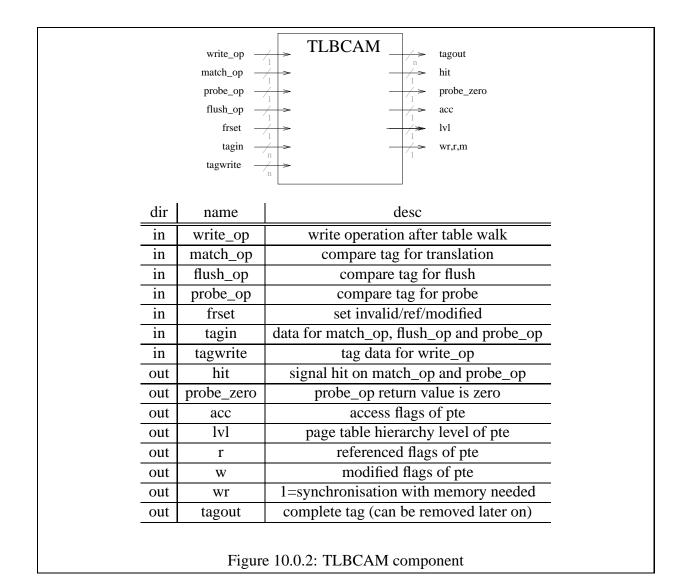

## 7.2.3 Translation Lookaside Buffer Entry (TLBCAM)

The TLB component is shown in figure 10.0.2.

The TLBCAM numbers can be configure from 2-32 entries. The TLBCAM components implement the concurrent comparison of the full associative TLB. It also implements the concurrent flush and probe operation<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup>In the current implementation the flush match logic, which is working concurrently inside TLBE, could be moved to TLBCAM because the flush operation is done one by one anyway (see figure 7.1.5). However this would require to add lines to access the TLBCAM 's tags which in turn would require a address decoder to access a specific tag out of the TLBCAM array. The "tagout" line of the TLBCAM component is doing just this, but it was only added for ASI space "MMU I/DCache diagnostic access" that can be removed later.

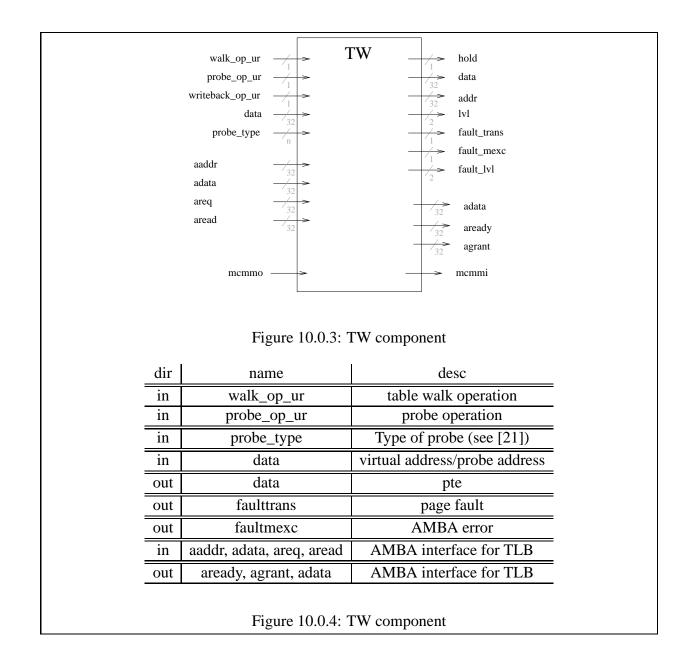

### 7.2.4 Table Walk (TW)

The TW component is shown in figure 10.0.4.

The main functions of the Table Walk component are:

- Perform a table walk on normal translation

- Perform a table walk on a probe operation

- AMBA interface, used for writeback operation of modified page table entries