# Bit-Flipping Scan - A Unified Architecture for Fault Tolerance and Offline Test

Imhof, Michael E.; Wunderlich, Hans-Joachim

Proceedings of the Design, Automation and Test in Europe (DATE'14) Dresden, Germany, 24-28 March 2014

doi: http://dx.doi.org/10.7873/DATE.2014.206

Abstract: Test is an essential task since the early days of digital circuits. Every produced chip undergoes at least a production test supported by on-chip test infrastructure to reduce test cost. Throughout the technology evolution fault tolerance gained importance and is now necessary in many applications to mitigate soft errors threatening consistent operation. While a variety of effective solutions exists to tackle both areas, test and fault tolerance are often implemented orthogonally, and hence do not exploit the potential synergies of a combined solution. The unified architecture presented here facilitates fault tolerance and test by combining a checksum of the sequential state with the ability to flip arbitrary bits. Experimental results confirm a reduced area overhead compared to a orthogonal combination of classical test and fault tolerance schemes. In combination with heuristically generated test sequences the test application time and test data volume are reduced significantly.

## **Preprint**

## General Copyright Notice

This article may be used for research, teaching and private study purposes. Any substantial or systematic reproduction, re-distribution, re-selling, loan or sub-licensing, systematic supply or distribution in any form to anyone is expressly forbidden.

This is the author's "personal copy" of the final, accepted version of the paper published by IEEE.<sup>1</sup>

©2014 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

<sup>&</sup>lt;sup>1</sup> IEEE COPYRIGHT NOTICE

## Bit-Flipping Scan - A Unified Architecture for Fault Tolerance and Offline Test

Michael E. Imhof, Hans-Joachim Wunderlich

Institute of Computer Architecture and Computer Engineering, University of Stuttgart Pfaffenwaldring 47, D-70569 Stuttgart, Germany, email: {imhof, wu}@informatik.uni-stuttgart.de

Abstract—Test is an essential task since the early days of digital circuits. Every produced chip undergoes at least a production test supported by on-chip test infrastructure to reduce test cost. Throughout the technology evolution fault tolerance gained importance and is now necessary in many applications to mitigate soft errors threatening consistent operation. While a variety of effective solutions exists to tackle both areas, test and fault tolerance are often implemented orthogonally, and hence do not exploit the potential synergies of a combined solution.

The unified architecture presented here facilitates fault tolerance and test by combining a checksum of the sequential state with the ability to flip arbitrary bits. Experimental results confirm a reduced area overhead compared to a orthogonal combination of classical test and fault tolerance schemes. In combination with heuristically generated test sequences the test application time and test data volume are reduced significantly.

Index Terms—Bit-Flipping Scan, Fault Tolerance, Test, Compaction, ATPG, Satisfiability

#### I. INTRODUCTION

The technology evolution of digital circuits is accompanied by two main challenges. To assure product quality offline test is a necessity. Under elevated soft error rates online fault tolerance constantly monitoring operation is of vital importance for reliability [1]. These two challenges require an *efficient hardware test* to cope with manufacturing defects as well as *fault tolerance* to confine transient errors caused by Single Event Upsets (SEUs) altering the sequential state.

Testing a circuit after production and throughout its lifetime to prove the presence of manufacturing defects or wearout effects is one of the most challenging areas in digital circuits. Testing sequential circuits without additional Design for Test (DfT) infrastructure is hard to achieve due to the limited access to the circuit state and the associated high complexity of sequential automatic test pattern generation (ATPG). The most widely adopted DfT infrastructure is scan design [2]. It provides observability and controllability of the circuit state by replacing sequential elements with scannable counterparts and grouping them into scan chains that are read and written sequentially. Nowadays multiple scan chains are used. The ability to use combinational test sets is paid by additional area overhead as well as increased test application times and test data volume. Although solutions like the use of multiple (shorter) scan chains or on-chip test data (de-)compression and compaction [3, 4, 5, 6] are able to reduce the test time and volume, they often substantially increase the area overhead in addition to the overhead introduced by the scan elements.

An alternative to scan-based DfT infrastructure is Random Access Scan (RAS) [7, 8]. It arranges the flip-flops of a circuit in an array providing unique access to read and write single

bits. In [9, 10] a toggle flip-flop is used to invert a bit instead of writing it. While still incorporating a high area overhead, the results show that significant savings in test time and volume are possible if the next test pattern is setup by selectively updating the captured circuit response.

Fault tolerance can be achieved by time, space or information redundancy. Due to the non-regular structure of random logic, most schemes protect the sequential state by a combination of time and space redundancy. The RAZOR approach [11] as well as the GRAAL scheme [12] duplicate each bit to detect SEUs and correct them by restoring the value from the shadow element. The area overhead inherent to bitwise duplication and comparison is reduced by using latches. If present, the scan portion can be reused to implement the shadow elements, however this implies that it runs at speed.

The work presented here targets the convergence of test and system reliability solutions by the following contributions:

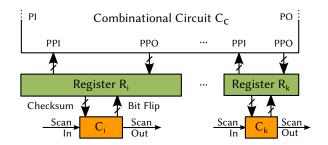

- A Unified Architecture (Fig. 1) utilizing information and structural redundancy. Each register  $R_i$  is extended with a checksum computation, a checksum register  $C_i$  and a mechanism to flip individual bits. Thereby enabling

- *Fault Tolerance* by effectively protecting the sequential state against SEUs.

- Test Access by observing compacted register states and controlling arbitrary register bits without the use of full scan.

Fig. 1. Presented Unified Architecture

• A heuristic for generating a **Bit-Flipping Scan Test Sequence** consisting of test patterns that validate the compacted sequential circuit state (test response) and setup the sequential state for the next test pattern with a minimized amount of bit-flips.

The next two sections detail the architecture and its use for fault tolerance and test access. Sections IV and V explain how the Bit-Flipping Scan test sequence generation is modeled as a satisfiability problem and solved heuristically.

#### II. ONLINE FAULT TOLERANCE ARCHITECTURE

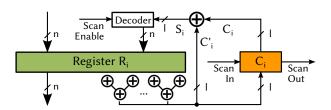

The online fault tolerance architecture from [13] is slightly extended to serve as the foundation for an efficient offline test. It protects the sequential state stored in registers against SEUs (Fig. 2). For each register  $R_i$  a combination of information and structural redundancy is employed to derive a resident checksum and store it in an additional register  $C_i$ . SEUs are detected by a signature  $S_i$  computed as the difference between the stored resident checksum and the checksum recomputed from the register values  $C'_i$ . Detected SEUs are localized by decoding the signature. Finally, the clock is gated and the affected register bit is corrected in one additional clock cycle with the help of a sequential standard cell that is inherently able to invert its internal state. False corrections due to SEUs in  $C_i$  are prevented by a parity of  $C_i$ . For offline testing scan design is added to  $C_i$  and the decoder is gated by the scan enable signal.

Fig. 2. Fault Tolerance Architecture with Test Extensions

The following subsections discuss the two main underlying concepts used to implement the fault tolerance: A) The area efficient *error detecting and correcting (EDAC) code* computation of the register content, and B) the efficient correction of SEUs at bit level employing *Bit-Flipping Flip-Flops*.

#### A. Error Detecting and Correcting Code

Let  $R_i$  be a register with n bits. Let  $R_i = [r_n, \cdots, r_1]^T$  represent the data word vector in matrix notation where  $r_{adr}$   $(n \ge adr \ge 1)$  references the bit at address adr. The modulo-2 address characteristic proposed in [14] is defined as the bitwise XOR of all addresses where  $r_{adr} = 1$ .  $r_0$  is not used, as address 0 does not contribute to  $C_i$ .

The mapping between data and characteristic bits corresponds to the generator matrix of a Hamming code and can be expressed by a modulo-2 characteristic matrix M.

$$M = \begin{bmatrix} a & & & \\ t^{2} & & & \\ & & & \end{bmatrix}$$

It consists of l rows and n columns, where n is the number of data bits and each column contains the binary address adr of the associated data bit. The maximum length over all used addresses defines the size of the calculated characteristic and depends on n logarithmically:

$$l = \lceil log_2(n+1) \rceil. \tag{1}$$

The characteristic  $C_i$  is computed by multiplying M with  $R_i$ :

$$C_i = M \cdot R_i$$

.

To detect an error, the characteristic of the original register content  $R_i$  is computed at time  $t_j$  and stored in an additional register  $C_i$  of size l. We call  $C_i$  the resident characteristic.

The recomputed characteristic  $C'_i$  is then concurrently derived from the register content  $R_i$  until new data is written. The difference between the resident characteristic  $C_i$  and the recomputed characteristic  $C'_i$  is called the signature of  $R_i$ :

$$S_i = C_i \oplus C'_i$$

.

If  $S_i$  is the all-zero vector no deviation was detected, otherwise  $S_i$  contains the address localizing the register bit affected by a single bit upset (SBU). The characteristic computation can be efficiently implemented using XOR2 standard cells [15].

Example: Let  $R_1$  be a 7-bit register with value  $\begin{bmatrix} 1011010 \end{bmatrix}^T$ . Together with the modulo-2 checksum matrix M, the resident characteristic  $C_1$  is computed and stored:

$$C_1 = M \cdot R_1 = \begin{bmatrix} 1 & 1 & 1 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 1 & 1 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 \end{bmatrix} \cdot R_1 = \begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}.$$

Now a SBU affects  $R_1$  and flips bit 5, resulting in the faulty register value  $R_1' = \begin{bmatrix} 1001010 \end{bmatrix}^T$ . The characteristic is recomputed as  $C_1'$  and the signature  $S_1$  is calculated:

$$C_1' = M \cdot R_1' = \begin{bmatrix} 0 \\ 0 \\ 1 \end{bmatrix} \quad S_1 = C_1 \oplus C_1' = \begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix} \oplus \begin{bmatrix} 0 \\ 0 \\ 1 \end{bmatrix} = \begin{bmatrix} 1 \\ 0 \\ 1 \end{bmatrix}.$$

As  $S_1$  is not zero the SBU is detected. Moreover  $S_1$  contains the address 5, thereby correctly localizing the SBU.

During offline test the characteristic is used for test response compaction.

#### B. Bit Flipping Flip-Flop

Whenever the signature  $S_i$  is not the zero vector it is decoded to a n-bit wide correction vector by a 1-out-of-n decoder. The vector then triggers the correction of the erroneous register bit while preserving the state of all other bits.

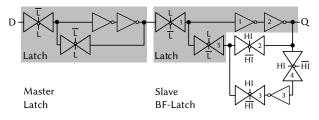

In contrast to the Bit-Flipping-Latch from [13], the Bit-Flipping Flip-Flop (Fig. 3) targets an edge-triggered design style. The master latch consists of two inverters (INV) and two transmission gates (TG). Both transmission gates are controlled by the control signal pair  $\{L, \overline{L}\}$ , selecting whether a new value is latched or the internal state is preserved.

Fig. 3. Bit-Flipping Flip-Flop: Schematic

The slave latch contains an additional inverting feedback loop (TG4, inverter INV3 and TG3) to flip the internal state. The new control signal pair  $\{HI, \overline{HI}\}$  for TG2 and TG3 selects either the original or the inverting feedback loop. To

avoid metastability of the inverting feedback loop, the inverter INV3 is precharged by TG4 if and only if the loop is not active. Inverting  $\{HI,\overline{HI}\}$  while the slave latch stores a value feeds the inverted value of Q to the inverter chain. If the inversion is canceled the non-inverting loop stores the inverted value.

The Bit-Flipping Flip-Flop can be implemented efficiently as a standard cell similar to the bit-flipping latch in [13].

#### III. OFFLINE TEST ACCESS ARCHITECTURE

The unified architecture is now used for test access to observe and control the sequential circuit state. Therefor the characteristic registers are equipped with scan design and the scan enable signal is used to gate the decoders (Fig. 2). Instead of directly observing the register content  $R_i$  in n cycles, the compacted characteristic in register  $C_i$  is observed in l cycles. To control  $R_i$  the bit-flipping capability inherent to the fault tolerance architecture is reused: Bit-flips are triggered at desired positions by shifting an appropriate characteristic into  $C_i$ . The efficiency of the accomplished test access depends on the ratio between n and l as well as the amount of bit-flips.

## A. Observing a Test Response

After setting up the stimulus for a test pattern p, the circuit response is captured into the internal registers R. In order to validate if the test pattern passed or failed the test response must be observed. The fault tolerance infrastructure already computes the resident characteristic of each  $R_i$  and stores it in the additional register  $C_i$  (Fig. 2). Instead of observing the captured response in  $R_i$  in n shift cycles,  $C_i$  is made scannable and the compacted circuit response is observed in l shift cycles, where  $l \ll n$  (Eq. 1).

The value of  $C_i$  depends on all bits of register  $R_i$  and represents a compacted version of the register content. It has the same properties as a response generated by a dedicated response compactor but reuses existing infrastructure. The characteristic has the same aliasing probability than other SECDED Hamming Codes [14]. It follows, that the compaction quality of Bit-Flipping Scan is comparable to methods like X-Compact [5] or EDT [3].

## B. Controlling a Register by Bit-Flipping

A mechanism to flip single bits of a register  $R_i$  is present in the architecture to correct SBUs in the fault tolerance mode. Now, this feature is used to setup the next state of register  $R_i$  by a series of bit-flips. For each pattern and bit-flip only l bits need to be shifted in, thereby reducing the complexity of the shift operation logarithmically from O(n) to  $O(log_2(n))$  (Eq. 1). Fig. 2 shows the involved architecture parts.

Let  $p_1$  and  $p_2$  be two test patterns, let  $O(R_i, p_1)$  denote the state of register  $R_i$  after the capture cycle of  $p_1$  with both characteristics  $C_i, C_i'$  being equal and let  $I(R_i, p_2)$  denote the state of  $R_i$  needed to setup  $p_2$ . Assume without loss of generality, that  $I(R_i, p_2)$  and  $O(R_i, p_1)$  differ in exactly one bit at address adr b  $(1 \le adr$   $b \le n)$ , and their Hamming distance is one. Then, the desired register value can be deduced by a single flip of the bit at adr b.

To trigger a bit-flip at this address the signature  $S_i$  needs to encode adr b:  $S_i = adr$  b. As the register state after  $p_1$  and the associated recomputed characteristic  $C'_i$  are known,

the resident characteristic  $C_i$  is computed as:  $C_i = S_i \oplus C_i'$ . Scanning in  $C_i$  triggers a bit-flip at adr b, generating  $I(R_i, p_2)$  from  $O(R_i, p_1)$  with l shift cycles and one additional cycle for the bit-flipping. At the same time, the compacted register state  $C_i$  is scanned out and observed. If the Hamming distance between the two register states is larger than one, a series of single bit-flips is used.

## C. Efficient Test Access

In traditional scan design the test application time depends on the maximum scan chain length n and the number of patterns. To apply a single pattern  $p_2$  the captured response  $O(R_i, p_1)$  of the previous pattern  $p_1$  is scanned out in n cycles while the desired state  $I(R_i, p_2)$  for  $p_2$  is shifted in concurrently. Then the circuit state is captured in one additional cycle:  $TAT_S = n + 1$ .

For the presented Bit-Flipping Scan scheme, the test time is dominated by the number of bit-flips bf. For each flip, l shift cycles and one flip cycle are needed. After applying all flips the circuit state is captured:  $TAT_{BFS} = bf \cdot (l+1) + 1$ .

Bit-Flipping Scan results in short test times. Formally, the maximum number of bit-flips at which both schemes have the same test time is defined by

$$\begin{split} \text{TAT}_{BFS} & \leq \text{TAT}_S \Leftrightarrow bf \cdot (l+1) + 1 \leq n+1 \\ \Leftrightarrow bf & \leq \frac{n}{l+1} \Leftrightarrow bf \leq \frac{n}{\lceil log_2(n+1) \rceil + 1} \end{split}$$

Example: For a maximum register size respectively scan chain length of 127 it follows that Bit-Flipping Scan has a lower test time if 15 or less flips per register and pattern are required ( $bf \le 15.875$ ).

Bit-Flipping Scan facilitates efficient test access by a logarithmic scan chain length reduction and altered scan chain semantics. Without loss of generality, classical test data (de-)compression and compaction schemes can be utilized to further improve test efficiency. The next sections show how the generation of optimized Bit-Flipping Scan test sequences is modeled and solved heuristically.

## IV. MODELING THE TEST SEQUENCE GENERATION

While in principle any test set can be applied using the test access provided by the unified architecture it is very likely to result in a suboptimal test time and volume due to a high number of involved bit-flips. The goal of efficiently utilizing the unified architecture for offline test is achieved by a tailored sequence of test patterns. After defining the properties of an globally optimal test sequence the reduction of sequential ATPG under bit-flips to a Boolean satisfiability problem and its modeling in conjunctive normal form (CNF) is discussed.

For a circuit C with a set of faults F, an optimal Bit-Flipping Scan test sequence  $P_{opt}$  ensures that

- all faults f in the fault universe F are detected by  $P_{opt}$

- the number of bit-flips to setup a register  $R_i$  for pattern  $p_j$  from the previous register state  $O(R_i, p_{j-1})$  is bound by  $HammingDist(O(R_i, p_{j-1}), I(R_i, p_j)) \leq bf_{bound}$

- the length of  $P_{opt}$  is minimal.

#### A. Circuit Modeling

A combinational representation  $C_C$  of C is built by removing all sequential elements and adding pseudo-primary in- and outputs (PPI/PPO). Each gate  $g_i \in C_C$  is then represented in CNF using the Tseitin encoding which generates a linear number of clauses at the cost of introducing a linear number of new variables [16]. Each gate  $g_i$  with inputs  $i_1, \dots, i_n$  and output o implementing a Boolean function  $o = \phi_g(i_1, \dots, i_n)$  is logically equivalent to  $\Phi_g =$  $(\overline{o} \lor \phi_g(i_1, \cdots, i_n)) \land (\overline{\phi_g(i_1, \cdots, i_n)} \lor o)$ . Expanding the equation in a product-of-sums form yields the set of clauses  $\Phi_q$  in CNF. The circuit  $C_C$  is then described in CNF as

$$\Phi_{C_C} = \bigwedge_{g_i \in C_C} \Phi_{g_i} \ .$$

## B. Modeling of Stuck-At Faults

Each stuck-at fault in F is represented as a new free literal f. The faulty circuit  $\Phi_{c'_f}$  is modeled by copying the output cone  $c_f$  of the fault site  $s_f$  and assigning new literals to the fault location and all other signals in the fault cone  $c'_f$  ( $s'_f$  for  $s_f$  and  $\forall s_n \in c_f : s'_n$ ). At the edge of the cone the according literals from  $\Phi_{C_C}$  are used. To generate a test pattern for fwith polarity  $p_f \in \{0, 1\}$  three conditions need to hold:

- Fault-free circuit: Fault site has the correct value:  $s_f = \overline{p_f}$

- Faulty circuit: Fault site has the faulty value:  $s_f'=p_f$  f is observed at least at one output:  $obs_f = \bigvee_{\forall (o,o') \in (c_f,c'_f)} (o \oplus o')$ .

Then fault f is modeled as

$$\begin{split} \Phi_f &= \Phi_{c_f'} \wedge \left( f \vee (\overline{s_f = \overline{p_f}}) \vee (\overline{s_f' = p_f}) \vee (\overline{obs_f}) \right) \wedge \\ & (\overline{f} \vee (s_f = \overline{p_f})) \wedge (\overline{f} \vee (s_f' = p_f)) \wedge (\overline{f} \vee obs_f) \ . \end{split}$$

#### C. Sequential Mapping and Modeling of Bit-Flips

The sequential behavior of  $C_S$  is modeled by unrolling. Each timeframe  $t_j$  is modeled by  $\Phi_{C_C,t_j}$  consisting of a copy of  $\Phi_{C_C}$  with appropriate literal renaming and  $\Phi_{f,t_j}$  denotes fault f in timeframe  $t_j$ .

Bit-Flips are modeled by introducing new free literals  $B(R_i, t_i)$  for each register  $R_i$ . Together with the pseudoprimary output literals  $O(R_i, t_{j-1})$  of the previous timeframe the sequential state in timeframe  $t_i$  is modeled:

$$\Phi^{B}_{t_{j-1},t_{j}} = \bigwedge_{\forall R_{i} \in C_{S}} (O(R_{i},t_{j-1}) \oplus B(R_{i},t_{j}) = I(R_{i},t_{j})) .$$

The sequential behavior under bit-flips is modeled as  $\Phi_B =$  $\wedge_{\forall j=1}^x(\Phi^B_{t_{j-1},t_j})$ . The number of bit-flips per register and timeframe is restricted by a cardinality constraint allowing 'atmost'  $bf_{bound}$  flip literals per register and timeframe to be

$$\Phi^{B_{card}}_{t_{j-1},t_j} = \bigwedge_{\forall R_i \in C_S} atmost(B(R_i, t_j), bf_{bound}) .$$

## D. Optimal Test Sequence $P_{opt}$

The SAT instance for the optimal test sequence  $P_{opt}$  from the beginning of this section can now be modeled as follows.

The circuit is unrolled for x timeframes:  $\Phi_{C_C} = \Phi_{C_C,t_1} \wedge$  $\cdots \wedge \Phi_{C_C,t_x}$ . All faults are added to each timeframe. As it is sufficient to detect a fault once, a disjunction over all timeframes is added per fault:  $\Phi_F = (\wedge_{\forall t_i \forall f} \Phi_{f,t_i}) \wedge$  $(\wedge_{\forall f}(\vee_{\forall t_i}(f(t_i))))$ . Between consecutive timeframes, bit-flip cardinality constraints are added to limit the maximum number of flips per register:  $\Phi_{B_{card}} = \wedge_{\forall j=1}^x (\Phi_{t_{j-1},t_j}^{B_{card}})$ . The literals of timeframe 0 are set to the registers initialization values:  $\Phi_0$ .

Solving the model  $\Phi_{opt} = \Phi_{C_C} \wedge \Phi_F \wedge \Phi_B \wedge \Phi_{B_{card}} \wedge \Phi_0$ yields a solution for x timeframes if it exists. The assignment of literals associated with primary in- and outputs in each timeframe  $t_i$  corresponds to a pattern  $p_i$ . The generated sequence detects all faults in F with at most  $bf_{bound}$  bit-flips per pattern (Sec. III-B). The test sequence  $P_{opt}$  with minimum length is found by bisection over the number of timeframes.

Finding the globally optimal test sequence is only feasible for small circuits, small fault universes and a limited number of timeframes due to the high complexity of ATPG and the associated runtimes [17]. Nonetheless an optimized Bit-Flipping Scan test sequence can be generated iteratively as depicted in the next section.

#### V. BIT-FLIPPING SCAN TEST SEQUENCE GENERATION

The heuristic iteratively generates patterns of the test sequence for combinationally detectable faults from the fault universe F, where each pattern p targets a limited number of not detected faults  $F_{nd}$ . All patterns are guaranteed to require a minimal number of bit-flips while covering the maximum amount of faults from  $F_{nd}$ . As a preprocessing step, F is classified by combinational ATPG and undetectable faults are removed. The remaining faults are sorted in descending order according to their testability, thereby putting preference on hard to detect faults in the iterative pattern generation.

The heuristic depicted in pseudocode in Algorithm 1 is invoked with the initialization pattern  $p_0$ , the fault universe F and the number of concurrently targeted faults maxF.

First, the SAT-model  $\Phi$  (l. 4) is built modeling one timeframe of the combinational circuit ( $\Phi_{C_C}$ ), the limited number of faults contained in  $F_{nd}$ , the bit-flips associated to the PPIs  $\Phi_B$  as well as cardinality constraint  $\Phi_{B_{numBF}}$  restricting the number of flips per register to numBF.

The for-loop (l. 6-14) searches for a pattern  $p_i$  covering a maximum number of faults numF from  $F_{nd}$ . In each iteration, for a given number of faults, a cardinality constraint is added to detect at least numF faults:  $\Phi_{numF} = atleast(F_{nd}, numF)$ . If the model is satisfiable under the current sequential state  $\Phi_{p_{i-1}}$ , pattern  $p_i$  is extracted and the loop continues with an increased numF. Once the model is not satisfiable, two cases need to be distinguished:

A pattern was found in an earlier iteration (l. 15): The current iteration proves that no pattern covering more faults from  $F_{nd}$  exists. The list of currently modeled faults  $F_{nd}$  and the global fault list F are pruned by fault simulation of p,  $p_i$  is added to the pattern sequence P and the bit-flip constraint  $\Phi_{numBF}$  is reset (l. 16-18). If more

## Algorithm 1 Iterative Bit-Flipping Scan ATPG

```

1: function GENERATEBFSPATTERNS(p_0, F, maxF)

ightharpoonup maxF not det. faults

F_{nd} \leftarrow getND(F, maxF)

P \leftarrow \emptyset \cup p_0; \ j \leftarrow 1; \ numBF \leftarrow 1

\Phi \leftarrow \Phi_{C_C} \wedge \Phi_{F_{nd}} \wedge \Phi_B \wedge \Phi_{B_{numBF}}

⊳ init, 1 BF per Reg.

3:

4:

while F \neq \emptyset do

5:

for numF \leftarrow 1, maxF do

6:

update(\Phi, \Phi_{numF})

7.

> add cardinality constraint

SAT \leftarrow solve(\Phi, \Phi_{p_{j-1}})

8:

\triangleright under seq. state of p_{i-1}

if SAT then

9:

10:

p_i \leftarrow extractPattern(\Phi); pFound \leftarrow true

11:

else

⊳ (line 6)

break for-loop

12:

13:

end if

end for

14:

15:

if pFound then

F \leftarrow fsim(p_i, F); F_{nd} \leftarrow fsim(p_i, F_{nd})

16:

▷ prune

P \leftarrow P \cup p_j; j \leftarrow j+1; pFound \leftarrow false

\triangleright add p

17:

numBF \leftarrow 1; update(\Phi, \Phi_{numBF})

18:

reset

if |F_{nd}| < 0.9 \cdot maxF then

□ update faults

19:

F_{nd} \leftarrow getND(F, maxF); update(\Phi, \Phi_{F_{nd}})

20:

21:

end if

22:

else

\triangleright no p under numBF

numBF \leftarrow numBF + 1; \ update(\Phi, \Phi_{B_{numBF}})

23:

24:

end if

25:

end while

return P

26:

27: end function

```

than 10% of the faults contained in  $F_{nd}$  are detected, the model is rebuilt with the next maxF faults (1. 20).

No pattern was found at all (1. 22): The iteration proves that no pattern detecting even a single fault exists under the constrained amount of bit-flips. numBF is increased and the for-loop is re-executed, thereby ensuring that the next pattern detects the maximum amount of modeled faults under the increased number of bit-flips.

The surrounding while loop (l. 5-25) terminates when all faults from F are detected. As F contains only combinationally detectable faults each fault in F will be detected, in the last resort by a pattern requiring a high amount of bit-flips.

## VI. EXPERIMENTAL EVALUATION

The presented scheme is evaluated for ISCAS89 and ITC99 benchmarks as well as for industrial circuits kindly provided by NXP (formerly Philips). For each circuit, the combinational core is synthesized for the  $45\ nm$  Nangate Open Cell Library (OCL) [18] using one- and two-input gates.

Four different scenarios are analyzed:

- a) Original: D-Flip-Flops (DFF,  $4.522 \,\mu m^2$ ).

- b) Scan Design: Scannable D-FFs (SDFFR,  $6.916 \,\mu m^2$ ).

- c) Fault Tolerance + Scan Design (FTScan): Scannable D-Flip-Flops together with a fault tolerance scheme comparable to RAZOR [11] or GRAAL [12]: A shadow latch (DLH,  $2.926 \, \mu m^2$ ), an exclusive OR (XOR2,  $1.596 \, \mu m^2$ ) and a multiplexer (MUX2,  $1.862 \, \mu m^2$ ).

- d) Bit-Flipping Scan (BFScan): Bit-Flipping Flip-Flops implemented as a new OCL-compatible standard cell (BFF,  $5.054 \, \mu m^2$ ) combined with the characteristic computation and the signature decoder as well as scannable characteristic registers (SDFFR,  $6.916 \, \mu m^2$ ).

For b) and c), all FFs are organized into scan chains with a maximum length of 127. For d), a register is implemented for each chain from the scan chain configuration used in b) and c). Note, that a chain length of 127 is rather short. For longer chains, scenarios b) and c) will scale linear in terms of area and test time. The area of the unified architecture and the test time of Bit-Flipping Scan sequences will grow slower due to the logarithmic correlation between n and l (Eq. 1).

#### A. Area Overhead

The gate area of the synthesized original circuit in  $\mu m^2$  is used as a baseline in Table I, corresponding gate counts can be found in columns 2 & 3 of Table II. The implementation of scan design increases the area (col. 3) and the area overhead to the original circuit is between 4.3% and 24.7% (col. 4). Implementing fault tolerance by bitwise redundancy orthogonal to scan design further increases the area (cols. 5 & 6). The area associated with the presented unified architecture (col. 7) is moderate for all circuits with an overhead between 21.7% and 81.8% (col. 8). The last column depicts the difference between the overheads of BFScan (col. 8) and FTScan (col. 6).

The results show, that compared to an orthogonal combination of the two classical methods, the unified architecture targeting both test and fault tolerance uses less area.

## B. Test Application Time

Table II compares the test application times. A highly compacted test set is generated for each FTScan configuration using a commercial ATPG. The heuristic from Section V is used to generate BFScan test sequences, where maxF was set to 100, providing a good tradeoff between runtime and achieved test time.

The total number of clock cycles for Bit-Flipping Scan is significantly lower compared to FTScan (col. 12 & 7) although the BFScan test sequence contains more patterns (cols. 8 & 4). Instead of n shift cycles only  $\lceil log_2(n+1) \rceil$  cycles are used per pattern and bit-flip, allowing to apply more patterns in

TABLE I Area Overhead for a max. Chain length/register size of 127

|         | Original  | Scan De   | FT + S | can       | Bit-Flipp | Area      |      |                    |

|---------|-----------|-----------|--------|-----------|-----------|-----------|------|--------------------|

| Circuit | (DFF)     | (SDFFR)   | ОН     | (SDFFR)   | ОН        | (BFFF)    | ОН   | $\Delta$ <b>OH</b> |

| name    | $\mu m^2$ | $\mu m^2$ | +%     | $\mu m^2$ | +%        | $\mu m^2$ | +%   | +%                 |

| (1)     | (2)       | (3)       | (4)    | (5)       | (6)       | (7)       | (8)  | (8)-(6)            |

| s35932  | 13461     | 16781     | 24.7   | 28946     | 115.0     | 24469     | 81.8 | -33.3              |

| s38417  | 14444     | 17883     | 23.8   | 29364     | 103.3     | 24344     | 68.5 | -34.8              |

| s38584  | 15744     | 18433     | 17.1   | 28582     | 81.5      | 24410     | 55.0 | -26.5              |

| b14     | 5252      | 5553      | 5.7    | 7390      | 40.7      | 6531      | 24.3 | -16.3              |

| b17     | 27606     | 30140     | 9.2    | 40096     | 45.2      | 36276     | 31.4 | -13.8              |

| b20     | 11048     | 11541     | 4.5    | 15016     | 35.9      | 13469     | 21.9 | -14.0              |

| b22     | 16531     | 17241     | 4.3    | 22740     | 37.6      | 20117     | 21.7 | -15.9              |

| p35k    | 27566     | 31971     | 16.0   | 45927     | 66.6      | 39649     | 43.8 | -22.8              |

| p45k    | 29346     | 33759     | 15.0   | 50125     | 70.8      | 43465     | 48.1 | -22.7              |

| p78k    | 57561     | 64935     | 12.8   | 83116     | 44.4      | 73647     | 27.9 | -16.5              |

| p100k   | 71177     | 82250     | 15.6   | 121278    | 70.4      | 104517    | 46.8 | -23.5              |

| p141k   | 128672    | 148146    | 15.1   | 220212    | 71.1      | 189140    | 47.0 | -24.1              |

| p239k   | 209954    | 243963    | 16.2   | 373044    | 77.7      | 317872    | 51.4 | -26.3              |

| p259k   | 246661    | 279568    | 13.3   | 419886    | 70.2      | 361851    | 46.7 | -23.5              |

| p267k   | 177598    | 210587    | 18.6   | 325096    | 83.1      | 276449    | 55.7 | -27.4              |

| p269k   | 177753    | 210564    | 18.5   | 325139    | 82.9      | 276912    | 55.8 | -27.1              |

| p279k   | 207302    | 240778    | 16.1   | 363884    | 75.5      | 311310    | 50.2 | -25.4              |

| p295k   | 211510    | 245279    | 16.0   | 372464    | 76.1      | 322304    | 52.4 | -23.7              |

| p330k   | 210958    | 244121    | 15.7   | 357882    | 69.6      | 308389    | 46.2 | -23.5              |

| p378k   | 287773    | 324514    | 12.8   | 413825    | 43.8      | 365445    | 27.0 | -16.8              |

| p418k   | 317313    | 371812    | 17.2   | 570179    | 79.7      | 489276    | 54.2 | -25.5              |

TABLE II TEST APPLICATION TIME (TAT) AND TEST DATA VOLUME (TDV) FOR A MAXIMUM CHAIN LENGTH/REGISTER SIZE OF 127

| Circuit                                                                                                            |                                                                                                                                | Test Application Time                                                                                                 |                                                                                                               |                                                                                                        |                                                                                                                                       |                                                                                                                                       |                                                                                                                  |                                                                                                          |                                                                                                                          |                                                                                                                                        | Test Data Volume                                                                                                                |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                          |                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                    | Gates                                                                                                                          |                                                                                                                       | Fault Tolerance + Scan Design                                                                                 |                                                                                                        |                                                                                                                                       |                                                                                                                                       | Bit-Flipping Scan                                                                                                |                                                                                                          |                                                                                                                          |                                                                                                                                        |                                                                                                                                 | TAT                                                                                                           |                                                                                                                                                                  |                                                                                                                                                          | TDV                                                                                                                        |

| name<br>(1)                                                                                                        | Comb.<br>count<br>(2)                                                                                                          | Seq.<br>count<br>(3)                                                                                                  | Pat.<br>count<br>(4)                                                                                          | Capture cycles (5)                                                                                     | Scan<br>cycles<br>(6)                                                                                                                 | Sum<br>cycles<br>(7)                                                                                                                  | Pat.<br>count<br>(8)                                                                                             | Capture cycles (9)                                                                                       | Flip<br>cycles<br>(10)                                                                                                   | Scan<br>cycles<br>(11)                                                                                                                 | Sum<br>cycles<br>(12)                                                                                                           | Speedup<br>ratio<br>(13)                                                                                      | FTScan<br>bits<br>(14)                                                                                                                                           | BFScan<br>bits<br>(15)                                                                                                                                   | Reduction % (16)                                                                                                           |

| s35932<br>s38417<br>s38584<br>b14<br>b17<br>b20<br>b22<br>p35k<br>p45k<br>p78k<br>p100k<br>p141k<br>p239k<br>p259k | 16065<br>23861<br>21938<br>10681<br>35482<br>21599<br>41443<br>38811<br>68263<br>84356<br>152808<br>224597<br>298796<br>238697 | 1728<br>1636<br>1452<br>245<br>1415<br>490<br>735<br>2173<br>2331<br>2977<br>5735<br>10501<br>18382<br>18398<br>16528 | 50<br>150<br>173<br>565<br>661<br>568<br>528<br>1068<br>2100<br>94<br>2050<br>612<br>517<br>672<br>724<br>726 | 50<br>150<br>173<br>565<br>661<br>568<br>528<br>1068<br>2100<br>94<br>2050<br>612<br>517<br>672<br>724 | 6477<br>19177<br>22098<br>71882<br>84074<br>72263<br>67183<br>135763<br>266827<br>12065<br>260427<br>77851<br>65786<br>85471<br>92075 | 6527<br>19327<br>22271<br>72447<br>84735<br>72831<br>67711<br>136831<br>268927<br>12159<br>262527<br>78463<br>66303<br>86143<br>92799 | 115<br>711<br>618<br>1293<br>2735<br>2043<br>2095<br>2726<br>3069<br>124<br>4356<br>1620<br>1663<br>2218<br>2834 | 115<br>711<br>618<br>1293<br>2735<br>2043<br>2095<br>2726<br>3069<br>124<br>4356<br>1623<br>2218<br>2834 | 114<br>716<br>626<br>1948<br>3952<br>2756<br>2558<br>2883<br>3216<br>123<br>5483<br>1621<br>1668<br>2218<br>2841<br>2841 | 805<br>5013<br>4389<br>12300<br>27437<br>18730<br>17732<br>20165<br>22504<br>868<br>38369<br>11354<br>11683<br>15533<br>19901<br>20279 | 1034<br>6440<br>5633<br>15541<br>34124<br>23529<br>22385<br>25774<br>28789<br>1115<br>48208<br>14595<br>15014<br>19969<br>25576 | 6.31<br>3.00<br>3.95<br>4.66<br>2.48<br>3.10<br>3.02<br>5.31<br>10.90<br>5.45<br>5.38<br>4.42<br>4.31<br>3.63 | 190550<br>510900<br>550672<br>325440<br>1959204<br>587312<br>804672<br>5490588<br>13206900<br>623408<br>24048550<br>13336704<br>19225490<br>25003776<br>24581972 | 63365<br>224531<br>281761<br>148259<br>812364<br>229981<br>294639<br>2838510<br>5799212<br>125488<br>3816114<br>3162100<br>4070658<br>5415952<br>7726117 | 66.75<br>56.05<br>48.83<br>54.44<br>58.54<br>60.84<br>63.38<br>48.30<br>56.09<br>79.87<br>84.13<br>76.29<br>78.83<br>78.34 |

| p269k<br>p279k<br>p295k<br>p330k<br>p378k<br>p418k                                                                 | 239771<br>257736<br>249747<br>312666<br>341315<br>382633                                                                       | 16528<br>17524<br>18465<br>16775<br>14885<br>28616                                                                    | 780<br>1579<br>1752<br>87<br>875                                                                              | 726<br>780<br>1579<br>1752<br>87<br>875                                                                | 92329<br>99187<br>200660<br>222631<br>11176<br>111252                                                                                 | 93055<br>99967<br>202239<br>224383<br>11263<br>112127                                                                                 | 2891<br>2912<br>6615<br>5071<br>234<br>3526                                                                      | 2891<br>2912<br>6615<br>5071<br>234<br>3526                                                              | 2896<br>2911<br>6614<br>5075<br>233<br>3527                                                                              | 20279<br>20384<br>46305<br>35532<br>1638<br>24696                                                                                      | 26066<br>26207<br>59534<br>45678<br>2105<br>31749                                                                               | 3.57<br>3.81<br>3.40<br>4.91<br>5.35<br>3.53                                                                  | 24650604<br>28002402<br>58468791<br>62157456<br>2884224<br>52707802                                                                                              | 7883099<br>8109920<br>14162715<br>19187520<br>1177020<br>21747326                                                                                        | 68.02<br>71.04<br>75.78<br>69.13<br>59.19<br>58.74                                                                         |

shorter time. Thus a raised coverage of non-target faults could be achieved, but needs to be investigated further.

The results show, that Bit-Flipping Scan results in a test application time speedup of 2.48X in the worst and up to 10.9X in the best case (col. 13).

#### C. Test Data Volume

The reported test data volume includes all bits exchanged with the circuit over primary and pseudo-primary in- and outputs. The test volume of Bit-Flipping Scan is lower for all circuits (col. 15 & 14). Column 16 depicts the achieved test volume reduction. For s35932, the test volume of BFScan is just 33.25% of the original volume. Thus Bit-Flipping Scan reduced the original volume by 66.75%.

The results show, that Bit-Flipping Scan reduces the test volume by between 48.3% and 84.13% of the original test volume (col. 16).

## VII. CONCLUSION

A unified architecture was presented that can be used for fault tolerance and offline test. It combines a checksum of the sequential circuit state with the ability to flip arbitrary bits. In fault tolerance, Single Event Upsets affecting the sequential elements are detected and located. A correction is performed in one additional clock cycle. In test, compacted test responses are observed and bit-flipping is used to derive the next test pattern from the captured state. The experimental results confirm a reduced area overhead due to the integrated consideration of fault tolerance and test. The presented test sequence generation heuristic successfully exploits the architectures capabilities and results in a significant reduction of test application time and test data volume.

#### VIII. ACKNOWLEDGMENT

Parts of this work were supported by the German Research Foundation (DFG) under grants WU 245/13-1 (RM-BIST). We would like to thank Manuel Jerger for his support.

#### REFERENCES

- International Technology Roadmap for Semiconductors (ITRS), 2012.

- M. J. Y. Williams and J. B. Angell, "Enhancing Testability of Large-[2] Scale Integrated Circuits via Test Points and Additional Logic," IEEE Transactions on Computers, vol. 22, pp. 46-60, 1973.

- J. Rajski, J. Tyszer, M. Kassab, et al., "Embedded deterministic test," IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 23, no. 5, pp. 776-792, 2004.

- N. A. Touba, "Survey of test vector compression techniques," IEEE Design & Test of Computers, vol. 23, no. 4, pp. 294-303, 2006.

- S. Mitra and K. S. Kim, "X-compact: an efficient response compaction technique," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 23, no. 3, pp. 421-432, 2004.

- M. A. Kochte, S. Holst, M. Elm, et al., "Test Encoding for Extreme Response Compaction," in IEEE Europ. Test Symp. (ETS), 2009, pp. 155-160.

- H. Ando, "Testing VLSI with random access scan," Proceedings of Compcon 80, pp. 50-52, 1980.

- D. H. Baik, K. K. Saluja, and S. Kajihara, "Random Access Scan: A solution to test power, test data volume and test time," in 17th International Conference on VLSI Design (VLSID), 2004, pp. 20-00.

- A. S. Mudlapur, V. Agrawal, and A. D. Singh, "A random access scan architecture to reduce hardware overhead," in IEEE International Test Conference (ITC), 2005, pp. 1-9.

- R. Adiga, G. Arpit, V. Singh, et al., "Modified T-Flip-Flop based scan cell for RAS," in *IEEE Europ. Test Symp. (ETS)*, 2010, pp. 113–118.

- D. Ernst, N. Kim, S. Das, et al., "Razor: a low-power pipeline based on circuit-level timing speculation," *IEEE/ACM International Symposium* on Microarchitecture, pp. 7-18, 2003.

- M. Nicolaidis, "GRAAL: a new fault tolerant design paradigm for mitigating the flaws of deep nanometric technologies," IEEE International Test Conference (ITC), pp. 1-10, 2007.

- M. E. Imhof and H.-J. Wunderlich, "Soft Error Correction in Embed-[13] ded Storage Elements," in 17th IEEE International On-Line Testing Symposium (IOLTS), 2011, pp. 169-174.

- V. N. Yarmolik, S. Hellebrand, and H.-J. Wunderlich, "Self-adjusting output data compression: An efficient BIST technique for RAMs," in Design, Automation and Test in Europe (DATE), 1998, pp. 173-179.

- M. E. Imhof, H.-J. Wunderlich, and C. G. Zoellin, "Integrating Scan Design and Soft Error Correction in Low-Power Applications," in 14th IEEE Intl. On-Line Testing Symposium (IOLTS), 2008, pp. 59-64.

- G. S. Tseitin, "On the Complexity of Derivation in Propositional Calculus," Studies in constructive mathematics and mathematical logic, vol. 2, no. 115-125, pp. 10-13, 1968.

- O. H. Ibarra and S. K. Sahni, "Polynomially complete fault detection problems," *IEEE Trans. on Comp.*, vol. 100, no. 3, pp. 242–249, 1975. "Nangate Open Cell Library v1.3," http://www.nangate.com.