# Mixed-Mode BIST Using Embedded Processors

SYBILLE HELLEBRAND, HANS-JOACHIM WUNDERLICH AND ANDRE HERTWIG

Division of Computer Architecture, University of Stuttgart, Breitwiesenstr. 20-22, 70565 Stuttgart, Germany

sybille@ramona.informatik.uni-stuttgart.de wu@informatik.uni-stuttgart.de andre.hertwig@informatik.uni-stuttgart.de

**Abstract.** In complex systems, embedded processors may be used to run software routines for test pattern generation and response evaluation. For system components which are not completely random pattern testable, the test programs have to generate deterministic patterns after random testing. Usually the random test part of the program requires long run times whereas the part for deterministic testing has high memory requirements.

In this paper it is shown that an appropriate selection of the random pattern test method can significantly reduce the memory requirements of the deterministic part. A new, highly efficient scheme for software-based random pattern testing is proposed, and it is shown how to extend the scheme for deterministic test pattern generation. The entire test scheme may also be used for implementing a scan based BIST in hardware.

Keywords: BIST, random pattern testing, deterministic BIST, embedded systems

## 1. Introduction

Integrating complex systems into single chips or implementing them as multi-chip modules (MCMs) has become a widespread approach. A variety of embedded processors and other embedded coreware can be found on the market, which allows to appropriately split the system functionality into both hardware and software modules. With this development, however, system testing and maintenance has become an enormous challenge: the complexity and the restricted accessibility of hardware components require sophisticated test strategies. Built-in self-test (BIST) combined with the IEEE 1149 standards can support both a low cost production test and efficient periodic maintenance tests [1]. The BIST equipment can further be used to test idle resources on-line during system operation.

For conventional ASIC testing, a number of powerful BIST techniques have been developed in the past [2–12]. For example, it has been shown that combining random and efficiently encoded deterministic patterns can provide complete fault coverage while keeping the cost for extra BIST hardware and the storage requirements low [13–15]. In the case of embedded systems such a high quality test is possible without any extra hardware by just using the embedded processor to generate the tests for all other components.

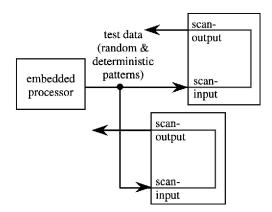

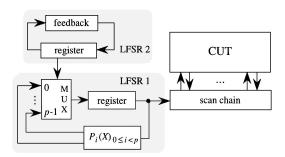

Usually, this kind of functional testing requires large test programs, and a memory space not always available on the system. In this paper it will be shown how small test programs can be synthesized such that a complete coverage of all non-redundant stuck-at faults in the combinational parts of the system is obtained. The cost for extra BIST hardware in conventional system testing is reduced to the cost of some hundred bytes of system memory to store the test routines. The proposed BIST approach can efficiently exploit design-for-testability structures of the subcomponents. As shown in Fig. 1 during serial BIST the embedded processor executes a program which generates test patterns and shifts them into the scan register(s) of the component(s) to be tested. Even more efficiently, the presented approach may be used to generate test data for input registers of pipelined or combinational subsystems.

The structure of the test program can be kept very simple, if only random patterns have to be generated,

Fig. 1. Serial BIST approach.

since then some elementary processor instructions can be used [16–19]. Even linear feedback shift registers (LFSRs) can be emulated very efficiently. But usually not all the subcomponents of a system will be random pattern testable, and for the remaining faults deterministic test patterns have to be applied. For this purpose, compact test sets may be generated as described in [20-23] and reproduced by the test program, or a hardwarebased deterministic BIST scheme is emulated by the test software [13-15, 24]. This kind of mixed-mode testing may interleave deterministic and random testing or perform it successively. In each case, the storage requirements for the deterministic part of the test program are directly related to the number of undetected faults after random pattern generation. There is a great trade-off between the run-time for the random test and the memory requirements of the mixed-mode program. Assume a small improvement of the random test method which leads to an increase of the fault coverage from 99.2% to 99.6%. This reduces the number of undetected faults and the storage requirements by the factor 1/2. Overall, the efficiency of a mixed-mode test scheme can be improved to a much higher degree by modifying its random part rather than its deterministic part [25].

In this paper a highly efficient software-based random BIST scheme is presented which is also used for generating deterministic patterns. The rest of the paper is organized as follows: In the next section, different random pattern test schemes to be emulated by software are evaluated, and in Section 3 the extension to deterministic testing is described. Subsequently, in Section 4, a procedure for optimizing the overall BIST scheme is presented, and Section 5 describes the procedure for generating the mixed-mode test program. Finally, Section 6 gives some experimental results based on the INTEL 80960CA processor as an example.

#### 2. Emulated Random Pattern Test

Test routines exploiting the arithmetic functions of a processor can produce patterns with properties which are sufficient for testing random pattern testable circuits [16, 18], even if they do not completely satisfy all the conditions for randomness as stated in [26]. However, for other circuits, in particular for circuits considered as random pattern resistant, arithmetic patterns may not perform as well. Linear feedback shift registers (LFSRs) corresponding to primitive feedback polynomials and cellular automata are generally considered as stimuli generators with good properties for random testing [27–29]. But the generated sequences still show some linear dependencies, such that different primitive polynomials perform differently on the same circuit. In some cases, the linear dependencies may support fault detection, for other circuits they perform poorly. In the following, the fault coverage obtained by several LFSR-based pattern generation schemes will be discussed with some experimental data.

## 2.1. Feedback Polynomial

In contrast to hardware-based BIST, in a softwarebased approach the number and the positions of the feedback taps of the LFSR have no impact on the cost of the BIST implementation. Thus, for a given length the achievable fault coverage can be optimized without cost constraints.

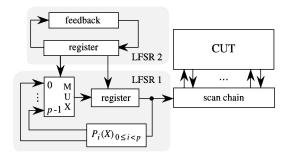

Assuming a test per scan scheme as shown in Fig. 2 the sensitivity of the fault coverage to the selected feedback polynominal has been studied by a series of experiments for the combinational parts of the ISCAS85 and ISCAS89 benchmark circuits [30, 31].

Fig. 2. Scan-based BIST.

| Circuit | P1  | F    | Degree | LFSR1  | LFSR2 | LFSR3  | LFSR4  | LFSR5  | LFSR6 | Average |

|---------|-----|------|--------|--------|-------|--------|--------|--------|-------|---------|

| c2670   | 157 | 2478 | 52     | 12.55  | 11.99 | 12.59  | 11.74  | 12.23  | 12.47 | 12.26   |

|         |     |      |        | 99.68  | 95.23 | 100.00 | 93.25  | 97.14  | 99.05 | 97.39   |

| c3540   | 50  | 3291 | 17     | 0.03   | 0.12  | 0.06   | 0.15   | 0.09   | 0.09  | 0.09    |

|         |     |      |        | 20.00  | 80.00 | 40.00  | 100.00 | 60.00  | 60.00 | 60.00   |

| s420.1  | 34  | 455  | 20     | 18.90  | 12.97 | 8.79   | 16.70  | 15.82  | 10.11 | 13.88   |

|         |     |      |        | 100.00 | 68.62 | 46.51  | 88.36  | 83.70  | 53.49 | 73.45   |

| s641    | 54  | 465  | 22     | 2.58   | 1.72  | 5.59   | 2.15   | 1.51   | 1.94  | 2.58    |

|         |     |      |        | 46.15  | 30.77 | 100.00 | 38.46  | 27.01  | 34.70 | 46.18   |

| s838.1  | 66  | 931  | 37     | 33.73  | 37.49 | 34.91  | 37.81  | 33.08  | 37.59 | 35.77   |

|         |     |      |        | 89.21  | 99.15 | 92.33  | 100.00 | 87.49  | 99.42 | 94.60   |

| s9234   | 247 | 6475 | 52     | 9.87   | 10.83 | 10.75  | 9.37   | 11.07  | 9.93  | 10.30   |

|         |     |      |        | 89.16  | 97.83 | 97.11  | 84.64  | 100.00 | 89.70 | 93.07   |

*Table 1.* Absolute and normalized (w.r.t. worst LFSR) percentage of undetected non-redundant faults after 10,000 patterns.

Fault simulation of 10,000 random patterns was performed for each circuit using several different feedback polynomials, all of the same degree. Some typical results are shown in Table 1.

The first four columns contain the circuit name, the number of inputs, the number of non-redundant faults and the selected degree of the feedback polynomial (the degrees of the polynomials have been selected, such that they were compatible with the requirements for the deterministic test described in Section 3). The remaining columns show the characteristics for six different LFSRs. The first entry reports the percentage of undetected non-redundant faults, and the second entry normalizes this number to the corresponding number for the worst LFSR (in %). The worst and best performing LFSR are printed in bold, respectively. The last column gives the average over all of the LFSRs.

It can be observed that there is a big variance in the performance of different LFSRs of the same degree. For s641, e.g., the best LFSR reduces the number of undetected faults down to 27% of the faults left undetected by the worst polynomial.

#### 2.2. Multiple-Polynomial LFSRs

One explanation for the considerable differences in fault coverage observed in Section 2.1 is given by the fact, that linear dependencies of scan positions may prevent certain necessary bit combinations in the scan patterns independent of the initial state of the LFSR [3]. For different LFSRs the distribution of linear dependencies in the scan chain is different and, depending on the structure of the circuit, may have a different impact on the fault coverage.

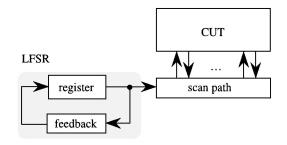

As shown in Fig. 3 the impact of linear dependencies can be reduced if several polynomials are used. In this small example the LFSR can operate according to two different primitive feedback polynomials  $P_0(X) = X^3 + X^2 + 1$  and  $P_1(X) = X^3 + X + 1$ , which are selected by the input *I* of the multiplexer. For any given initial state  $(x_0, x_1, x_2)$  the LFSR produces a scan pattern  $(a_0, \ldots, a_7)$ , such that, depending on the selected polynomial, the shown equations for  $P_0(X)$  or  $P_1(X)$  hold for its components.

Fig. 3. Scan-based BIST with multiple-polynomial LFSR.

| initialize (LFSR);                                    |

|-------------------------------------------------------|

| for $(i = 0; i < p; i++)$                             |

| generate $[N / p]$ patterns by LFSR(P <sub>i</sub> ); |

| Fig. 4. Successive multiple-polynomial scheme (SUC).  |

For polynomial  $P_0$  there is a linear relation  $a_3 + a_5 = x_0 + x_2 + x_0 + x_1 = x_1 + x_2 = a_7$ , which prevents the combination (1, 1, 1) at the inputs of the ANDgate. This implies that the polynomial  $P_0(X)$  can never produce a test for the stuck-at-0 fault at node  $o_2$ . In contrast to that, for polynomial  $P_1(X)$  the same input positions are linearly independent and produce all possible nonzero bit combinations and thus a test for the considered fault. Similarly, the stuck-at-0 fault at node  $o_1$  cannot be tested using polynomial  $P_1(X)$ , but polynomial  $P_0(X)$  can provide a test. Using both polynomials, each for a certain number of patterns, increases the chance of detecting both faults.

Such a multiple-polynomial LFSR can be implemented efficiently in hardware by sharing parts of the feedback for several polynomials. A software emulation is also very simple, since the basic procedure to simulate an LFSR has to be modified only slightly. To control the selection of feedback polynomials several schemes are possible. The first is shown in Fig. 4 assuming N random patterns to be generated by p different polynomials  $P_i$ , i = 0, ..., p - 1. LFSR( $P_i$ ) denotes the LFSR operation corresponding to feedback polynomial  $P_i$ .

The polynomials are applied successively to generate contiguous subsequences of  $\lceil N/p \rceil$  random patterns, the scheme will therefore be referred to as scheme SUC. For one polynomial the scheme degenerates to the conventional single polynomial scheme. The possibility to switch between different distributions of linear dependencies is paid by the disadvantage that some patterns may occur repeatedly up to *p* times. Hence, an overall increase of the fault coverage cannot be expected, but experiments have shown that there is indeed an improvement for some circuits. Table 2 lists the results for the same set of circuits as studied in the previous section.

For each circuit 10,000 patterns were simulated using p = 2, ..., 5 polynomials. For each experiment the percentage of undetected non-redundant faults is reported (1st line), as well as the corresponding normalized numbers for the worst (2nd line) and for the best single polynomial (3rd line) of the same degree (in %).

Applying the successive scheme for example to the circuit c2670 with p = 4 reduces the number of

*Table 2.* Absolute and normalized (w.r.t. worst and best single LFSR) percentage of undetected non-redundant faults for scheme SUC after 10,000 patterns.

| <i>p</i> = 5 | p = 4  | p = 3  | p = 2  | Degree | Circuit |

|--------------|--------|--------|--------|--------|---------|

| 12.55        | 8.76   | 12.55  | 12.55  | 52     | c2670   |

| 99.68        | 69.58  | 99.68  | 99.68  |        |         |

| 106.90       | 74.62  | 106.90 | 106.90 |        |         |

| 0.12         | 0.09   | 0.12   | 0.03   | 17     | c3540   |

| 80.00        | 60.00  | 80.00  | 20.00  |        |         |

| 400.00       | 300.00 | 400.00 | 100.00 |        |         |

| 12.97        | 13.41  | 14.51  | 14.95  | 20     | s420.1  |

| 68.62        | 70.95  | 76.77  | 79.10  |        |         |

| 147.55       | 152.56 | 165.07 | 170.08 |        |         |

| 1.72         | 1.94   | 1.94   | 1.94   | 22     | s641    |

| 30.77        | 34.70  | 34.70  | 34.70  |        |         |

| 113.91       | 128.48 | 128.48 | 128.48 |        |         |

| 30.18        | 31.26  | 31.26  | 30.72  | 37     | s838.1  |

| 79.82        | 82.68  | 82.68  | 81.25  |        |         |

| 91.23        | 94.50  | 94.50  | 92.87  |        |         |

| 9.22         | 10.13  | 10.67  | 10.61  | 52     | s9234   |

| 83.29        | 91.51  | 96.39  | 95.84  |        |         |

| 98.40        | 108.11 | 113.87 | 113.23 |        |         |

undetected faults down to 69.58% compared with the worst single polynomial. Even more important is that the scheme also outperforms the best single polynomial and the number of remaining target faults for ATPG is less than 75%, i.e., 25% of the faults left by the best single polynomial are additionally covered by this scheme.

The randomness of the sequence can be further increased, if the polynomials are not used successively, but selected randomly for each test pattern. This random selection can be implemented by a second LFSR as shown in Fig. 5 and will be referred to as scheme RND.

*Fig.* 5. Hardware scheme for the random selection of feedback polynomials (RND).

```

initialize (LFSR1);

initialize (LFSR2);

for (i = 0; i < N; i++)

{

select P based on state of LFSR2;

generate 1 pattern by LFSR1(P);

perform 1 state transition of LFSR2;

}

```

*Fig. 6.* Software routine for the random pattern generation scheme of Fig. 5 (RND).

The selection between p different feedback polynomials for LFSR1 is controlled by  $\lceil \log_2 p \rceil$  bits of the state register of LFSR2. For a software implementation of the structure of Fig. 5, two additional registers are required for storing the feedback polynomial and the state of LFSR2. LFSR1 and LFSR2 can be emulated by the same procedure, and the complete routine to generate a sequence of N random patterns is shown in Fig. 6.

Table 3 shows the percentage of undetected nonredundant faults and the corresponding normalized

*Table 3.* Absolute and normalized (w.r.t. worst and best single LFSR) percentage of undetected non-redundant faults for scheme RND after 10,000 patterns.

| Circuit | Degree | p = 2  | p = 3  | p = 4  | <i>p</i> = 5 |

|---------|--------|--------|--------|--------|--------------|

| c2670   | 52     | 12.63  | 12.35  | 11.99  | 12.55        |

|         |        | 100.32 | 98.09  | 95.23  | 99.68        |

|         |        | 107.58 | 105.2  | 102.13 | 106.90       |

| c3540   | 17     | 0.06   | 0.09   | 0.09   | 0.12         |

|         |        | 40.00  | 60.00  | 60.00  | 80.00        |

|         |        | 200.00 | 300.00 | 300.00 | 400.00       |

| s420.1  | 20     | 12.75  | 14.51  | 14.29  | 17.14        |

|         |        | 67.46  | 76.77  | 75.61  | 90.69        |

|         |        | 145.05 | 165.07 | 162.57 | 194.99       |

| s641    | 22     | 1.72   | 1.94   | 1.94   | 1.51         |

|         |        | 30.77  | 34.70  | 34.70  | 27.01        |

|         |        | 113.91 | 128.48 | 128.48 | 100.00       |

| s838.1  | 37     | 38.56  | 33.40  | 36.95  | 36.84        |

|         |        | 101.98 | 88.34  | 97.73  | 97.43        |

|         |        | 116.57 | 100.97 | 111.70 | 111.37       |

| s9234   | 52     | 9.61   | 11.24  | 10.16  | 10.75        |

|         |        | 86.81  | 101.54 | 91.78  | 97.11        |

|         |        | 102.56 | 119.96 | 108.43 | 114.73       |

numbers obtained by the scheme RND for p = 2, ..., 5 feedback polynomials.

For the randomly selected polynomials, there is a higher chance of pattern repetitions, but randomly switching between different distributions of linear dependencies may improve the quality of the patterns. For some circuits, this results in an improvement of fault coverage, so that the set of faults which remain for deterministic testing is further reduced.

## 2.3. Multiple-Polynomial, Multiple-Seed LFSRs

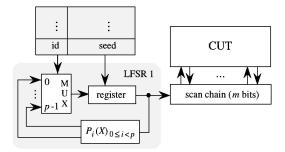

Another way of improving the efficiency of a random test is repeatedly using a new seed during pattern generation as investigated for instance in [32]. This technique can be combined with the use of multiple polynomials as shown in Fig. 7.

As for the scheme RND,  $\lceil \log_2 p \rceil$  bits of the state register of LFSR2 are used to drive the selection between p different feedback polynomials of degree k for LFSR1. The remaining k bits provide the seed for LFSR1. In the sequel this scheme will be referred to as the scheme RND<sup>2</sup>. The structure of the corresponding test program is shown in Fig. 8.

Again, in this scheme patterns may occur repeatedly, but in addition to the advantage of randomly changing

Fig. 7. Multiple-polynomial, multiple-seed LFSR.

```

initialize (LFSR2);

for (i = 0; i < N; i++)

{

select seed S and polynomial P

based on state of LFSR2;

initialize LFSR1 with S;

generate 1 pattern by LFSR1 (p);

perform 1 state transition of LFSR2;

}

```

*Fig.* 8. Test program for the multiple-polynomial, multiple-seed LFSR (RND<sup>2</sup>).

| Circuit | Degree | p = 2  | p = 3  | p = 4  | p = 5  |

|---------|--------|--------|--------|--------|--------|

| c2670   | 52     | 12.31  | 12.15  | 12.15  | 12.55  |

|         |        | 97.78  | 96.51  | 96.51  | 99.68  |

|         |        | 104.86 | 103.49 | 103.49 | 106.90 |

| c3540   | 17     | 0.12   | 0.18   | 0.18   | 0.18   |

|         |        | 80.00  | 120.00 | 120.00 | 120.00 |

|         |        | 400.00 | 600.00 | 600.00 | 600.00 |

| s420.1  | 20     | 12.31  | 13.19  | 12.75  | 10.99  |

|         |        | 65.13  | 69.79  | 67.46  | 58.15  |

|         |        | 140.05 | 150.06 | 145.05 | 125.03 |

| s641    | 22     | 1.94   | 1.94   | 1.94   | 2.15   |

|         |        | 34.70  | 34.70  | 34.70  | 38.46  |

|         |        | 128.48 | 128.48 | 128.48 | 142.38 |

| s838.1  | 37     | 27.71  | 23.52  | 23.52  | 26.53  |

|         |        | 73.29  | 62.21  | 62.21  | 70.17  |

|         |        | 83.77  | 71.10  | 71.10  | 80.20  |

| s9234   | 52     | 9.14   | 9.85   | 9.58   | 9.58   |

|         |        | 82.57  | 88.98  | 86.54  | 86.54  |

| _       |        | 97.55  | 105.12 | 102.24 | 102.24 |

*Table 4.* Absolute and normalized (w.r.t. worst and best single LFSR) percentage of undetected non-redundant faults for scheme  $\text{RND}^2$  after 10,000 patterns.

the distribution of linear dependencies this scheme is also able to generate the all zero-vector which is often needed for complete fault coverage.

Table 4 gives the results for p = 2, ..., 5 polynomials (percentage of undetected non-redundant faults and the corresponding normalized numbers as in Tables 2 and 3).

As expected, not for all circuits the fault coverage increases, but there are circuits where this technique leads to significant improvements. For circuits s838.1 and s9234 the best results are obtained compared with all the experiments before.

#### 3. Software-Based Deterministic BIST

The structure of the multiple-polynomial, multipleseed random BIST scheme of Fig. 7 is very similar to the deterministic BIST scheme based on reseeding of multiple-polynomial LFSRs proposed in [13, 14], see Fig. 9.

A deterministic pattern is encoded as a polynomial identifier and a seed for the respective polynomial. During test mode the pattern can be reproduced by emulating the LFSR corresponding to the polynomial

*Fig. 9.* Deterministic BIST scheme based on a multiplepolynomial LFSR by [14].

identifier, loading the seed into the LFSR and performing *m* autonomous transitions of the LFSR. After the *m*th transition the scan chain contains the desired pattern which is then applied to the CUT.

To calculate, the encoding systems of linear equations have to be solved. For a fixed feedback polynomial  $h(X) = X^{k} + h_{k-1}X^{k-1} + \dots + h_{1}X + h_{0}$  of degree k the LFSR produces an output sequence  $(a_i)_{i>0}$ satisfying the feedback equation  $a_i = a_{i-1} \cdot h_{k-1} + \cdots + a_{k-1} + \cdots + a_{k-1}$  $a_{i-k} \cdot h_0$  for all  $i \ge k$ . The LFSR-sequence is compatible with a desired test pattern  $t = (t_1, \ldots, t_m)$ , if for all specified bits  $a_i = t_i$  holds. Recursively applying the feedback equation provides a system of linear equations in the seed variables  $a_0, \ldots, a_{k-1}$ . If no solution can be found for the given polynomial, the next available polynomial is tried, and in [14] it has been shown that already for 16 polynomials there is a very high probability of success that a deterministic pattern with s specified bits can be encoded into an s-bit seed.

Hence, if p different polynomials are available and the polynomial identifier is implemented as a "next bit", the seed and the next bits for a deterministic test set  $T = \{t_1, \ldots, t_N\}$  with maximum number of specified bits  $s_{\text{max}}$  require  $S(T) := (s_{\text{max}} + 1) \cdot N$  bits of storage. Minimizing S(T) requires both minimizing the maximum number of care bits  $s_{\text{max}}$  and the number of patterns N. In [24] an ATPG-algorithm was presented which generates test patterns where the number of specified bits  $s_{\text{max}}$  is minimized. In a mixed-mode BIST approach the number N of patterns is highly correlated to the number of faults left undetected after random testing.

#### 4. Synthesizing the BIST Scheme

Since the efficiency of a mixed-mode BIST scheme strongly depends on the number of hard faults to be

covered by deterministic patterns, a major concern in synthesizing the BIST scheme is optimizing the random test. The experimental data of Section 2 show that significant variances in the fault efficiency achieved by different LFSR schemes exist, and that there is no universal scheme or polynomial working for all of the circuits. In the sequel, a procedure is presented for determining an optimized LFSR scheme. The selection of the LFSRs is guided, such that the fault efficiency is maximized while satisfying the requirements for an efficient encoding of deterministic patterns for the random pattern resistant faults. Assuming a table of primitive polynomials available the proposed procedure consists of four steps:

- (1) Perform ATPG to eliminate the redundant faults and to estimate the maximum number of specified bits,  $s_{max}$ , to be expected in the test cubes for the hard faults.

- (2) Select M polynomials of degree  $s_{\text{max}}$  randomly, and perform fault simulation with the corresponding shift register sequences. Rank the polynomials according to the fault coverage achieved.

- (3) Select the *P* best polynomials and store the highest fault coverage and the corresponding LFSR as BEST\_SCHEME.

- (4) Using 2≤p≤P polynomials, simulate the schemes SUC, RND, and RND<sup>2</sup>. Update BEST\_SCHEME to the best solution obtained so far.

The number M is mainly determined by a limit of the computing time to be spent. The number P is also restricted by the computing time available, but in addition to that each LFSR requires two registers of the processor for pattern generation. So, the register file of the target processor puts a limit on P, too.

Table 5 shows the results achieved by this procedure for the same set of circuits as studied in Section 2. For the same degrees as used in Section 2 sequences of 10,000 random patterns were applied.

The second and third column show the best scheme and the corresponding number of polynomials p, column 4 provides the fault efficiency FE (percentage of detected non-redundant faults). The percentage of faults left undetected by the best scheme is reported in column UF. UF<sub>best</sub> normalizes this solution to the number obtained by the best single polynomial, UF<sub>worst</sub> refers to the worst single polynomial.

Table 5 indicates that the search for an appropriate random test scheme can reduce the number of remaining faults significantly. The procedure needs

*Table 5.* Best schemes and relation to best and worst single polynomial solution.

| Circuit | Best<br>scheme   | р | FE    | UF    | UF <sub>best</sub> | UF <sub>worst</sub> |

|---------|------------------|---|-------|-------|--------------------|---------------------|

| c2670   | SUC              | 4 | 91.24 | 8.76  | 74.62              | 69.58               |

| c3540   | SUC              | 2 | 99.97 | 0.03  | 100.00             | 20.00               |

| s420.1  | SUC              | 1 | 91.21 | 8.79  | 100.00             | 63.33               |

| s641    | RND              | 5 | 98.49 | 1.51  | 100.00             | 27.01               |

| s838.1  | RND <sup>2</sup> | 3 | 76.48 | 23.52 | 71.10              | 62.21               |

| s9234   | RND <sup>2</sup> | 2 | 90.86 | 9.14  | 97.55              | 82.57               |

$M + 3 \cdot (P - 1)$  runs of fault simulations, but may decrease the storage amount needed for deterministic patterns considerably. These savings in memory for the mixed-mode test program are particularly important, if the test program has to be stored in a ROM for start-up and maintenance test.

## 5. Generating Mixed-Mode Test Programs

Test programs implementing the random test schemes and the reseeding scheme for deterministic patterns were generated for the INTEL 80960CA as a target processor. Since the part of the test program which generates the deterministic patterns is a superset of instructions required for implementing any of the random schemes, only the example for the most complex random scheme is shown. The mixed-mode test program of Fig. 10 generates random test patterns by multiple-polynomial, multiple-seed LFSR emulation, and switches to the reseeding scheme afterwards.

The program of Fig. 10 requires 27 words in memory but assumes that all LFSRs fit into 32 bits registers. This is always possible for random pattern generation, but encoding deterministic patterns may lead to LFSR lengths exceeding 32 bits. In this case, the program of Fig. 10 has to be modified in a straightforward way, and requires more memory. Table 6 gives the relation between memory requirements and LFSR lengths.

*Table 6.* LFSR length and memory requirements for the mixed-mode test program.

| LFSR length                    | 32 | 64 | 96 | 128 |

|--------------------------------|----|----|----|-----|

| Memory requirements<br>(words) | 27 | 41 | 52 | 63  |

| at an a 1    |         |                                          |   | number of store for literal              |

|--------------|---------|------------------------------------------|---|------------------------------------------|

| steps1       | equ     |                                          |   | number of steps for lfsrl                |

| steps2       | equ     | •••                                      |   | number of steps for lfsr2                |

| steps_det    | equ     | •••                                      |   | number of steps for deterministic test   |

| len1         | equ     | •••                                      |   | position of msb of lfsr1                 |

| len2         | equ     | •••                                      |   | position of msb of lfsr2                 |

| testport     | equ     | •••                                      |   | address of testport                      |

| no_poly_bits | -       | •••                                      |   | number of bits for polynomial choice     |

| mask         | equ     | •••                                      |   | define mask                              |

| start        | dq      | startvector                              |   | define startvector for lfsr2             |

| poly         | dq      | polynomials                              |   | define polynomials for lfsr1             |

|              |         |                                          |   | and lfsr2 (poly[0])                      |

| seeds        | dq      | seedvectors                              |   | define seeds for deterministic test      |

| seed_offset  | equ     | seeds – start                            | ; | define offset for seed table             |

| begin:       | lda     | testport, r10                            | ; | load address of testport                 |

|              | lda     | steps_det, r11                           | ; | load loop counter for lfsr1 in det. mode |

|              | lda     | steps1, r12                              | ; | load loop counter for lfsr1              |

|              | lda     | start, r14                               | ; | load startvector address for lfsr1       |

|              | ld      | (r14), r6                                | ; | load startvector for lfsr2               |

|              | ld      | 4(r14), r7                               | ; | load polynomial for lfsr2                |

| 10:          | mov     | r6, r4                                   | ; | initialize lfsr1 with contents of lfsr2  |

|              | and     | mask, r4, r15                            | ; | compute poly-id                          |

|              | ld      | 8(r14) [r15*4], r5                       | ; | load polynomial for lfsr1                |

|              | lda     | no_poly_bits, r15                        | ; | load number of bits for poly-id          |

| 11:          | shro    | no_poly_bits, r4, r4                     | ; | shift poly-bits                          |

|              | lda     | steps2, r13                              | ; | load loop counter for lfsr1              |

| 12:          | st      | r4, (r10)                                | ; | write testpattern to testport            |

|              | mov     | r4, r8,                                  |   |                                          |

|              | shlo    | 1, r8, r4                                | ; | shift left                               |

|              | bbc     | len2, r8, 13                             | ; | branch if msb of lfsr2 equal zero        |

|              | xor     | r4, r5, r4                               | ; | xor                                      |

| 13:          | subi    | r13, 1, r13                              | ; | decrement loop counter                   |

|              | cmpibne | r13, 0, 12                               | ; | branch not equal zero                    |

|              | mov     | r6, r8                                   |   |                                          |

|              | shlo    | 1, r8, r6                                | ; | shift left                               |

|              | bbc     | len1, r8, 14                             | ; | branch if msb of lfsr1 equal zero        |

|              | xor     | r6, r7, r6                               | ; | xor                                      |

| 14:          | subi    | r12, 1, r12                              | ; | decrement loop counter                   |

|              | cmpibg  | r12, r11, 10                             | ; | branch if r12 > steps_det                |

|              | ld      | <pre>seed_offsets(r14) [r12*4], r6</pre> | ; | load seed                                |

|              | cmpibne | r12, 0, 10                               |   |                                          |

|              |         |                                          |   |                                          |

Fig. 10. Mixed-mode BIST program.

In addition to the program size, memory has to be reserved for storing the polynomials and the seeds in order to decode the deterministic patterns. The experimental results of the next section show that these data form by far the major part of the memory requirements.

## 6. Experimental Results

The described strategy for generating mixed-mode test programs was applied to all the benchmark circuits for M = 16 and P = 5, i.e., for each circuit  $M + 3 \cdot (P - 1) = 28$  runs of fault simulation were performed

*Table 7.* Circuit characteristics and best random scheme.

| Circuit | PI   | Degree | Best scheme      | р |

|---------|------|--------|------------------|---|

| c2670   | 157  | 52     | SUC              | 4 |

| c3540   | 50   | 19     | SUC              | 2 |

| c7552   | 206  | 106    | RND <sup>2</sup> | 3 |

| s420.1  | 34   | 20     | SUC              | 1 |

| s641    | 54   | 22     | SUC              | 1 |

| s713    | 54   | 22     | SUC              | 1 |

| s820    | 23   | 15     | SUC              | 5 |

| s832    | 23   | 15     | RND <sup>2</sup> | 5 |

| s838.1  | 66   | 37     | RND <sup>2</sup> | 3 |

| s953    | 45   | 15     | SUC              | 1 |

| s1196   | 32   | 17     | RND <sup>2</sup> | 2 |

| s1238   | 32   | 17     | RND <sup>2</sup> | 2 |

| s1423   | 91   | 25     | $RND^2$          | 5 |

| s5378   | 214  | 25     | RND              | 5 |

| s9234   | 247  | 52     | RND <sup>2</sup> | 2 |

| s13207  | 700  | 60     | SUC              | 5 |

| s15850  | 611  | 48     | SUC              | 2 |

| s38417  | 1664 | 106    | $RND^2$          | 4 |

| s38584  | 1464 | 60     | SUC              | 2 |

to determine the best random scheme. Tables 7 and 8 show the results.

The selected random schemes and their characteristic data are reported in Table 7. Columns 2 and 3 list the number of primary inputs PI and the degree of the polynomials. The best random scheme and the number of polynomials p are reported in the subsequent columns.

Table 8 shows the detailed results. The number of non-redundant faults for each circuit is given in column 2. The efficiency of the random scheme is characterized again by the fault efficiency FE, the percentage of undetected non-redundant faults UF and the normalized numbers for UF with respect to the best (UF<sub>best</sub>) and the average (UF<sub>average</sub>) single polynomial solution in columns 3 through 6.

The reduction of the remaining faults obtained by the best random test scheme is significant. For instance, the circuit c7552 is known to be very random pattern resistant, and a single polynomial solution in the average leads to a fault efficiency of 95.79% leaving 4.21% of the faults for deterministic encoding. For the same circuit, the RND<sup>2</sup> scheme achieves a fault efficiency of 98.87%, and only 1.13% or, absolutely, 84 faults are

*Table 8.* Fault efficiency and percentage of undetected nonredundant faults for the best random schemes after 10,000 patterns.

| Circuit | F     | FE     | UF    | UFbest | UFaverage |

|---------|-------|--------|-------|--------|-----------|

| c2670   | 2478  | 91.24  | 8.76  | 74.62  | 71.45     |

| c3540   | 3291  | 99.97  | 0.03  | 100.00 | 33.33     |

| c7552   | 7419  | 98.87  | 1.13  | 30.46  | 26.84     |

| s420.1  | 455   | 91.21  | 8.79  | 100.00 | 63.33     |

| s641    | 465   | 98.49  | 1.51  | 100.00 | 27.01     |

| s713    | 543   | 98.71  | 1.29  | 100.00 | 70.11     |

| s820    | 850   | 100.00 | _     | _      | _         |

| s832    | 856   | 99.77  | 0.23  | 24.73  | 4.21      |

| s838.1  | 931   | 76.48  | 23.52 | 71.10  | 65.75     |

| s953    | 1079  | 99.26  | 0.74  | 100.00 | 18.50     |

| s1196   | 1242  | 99.28  | 0.72  | 68.57  | 40.91     |

| s1238   | 1286  | 99.38  | 0.62  | 66.67  | 35.43     |

| s1423   | 1501  | 100.00 | _     | _      | _         |

| s5378   | 4563  | 99.45  | 0.55  | 85.94  | 61.8      |

| s9234   | 6475  | 90.86  | 9.14  | 97.55  | 88.74     |

| s13207  | 9664  | 94.45  | 5.55  | 89.95  | 80.79     |

| s15850  | 11336 | 94.89  | 5.11  | 94.28  | 89.96     |

| s38417  | 31015 | 93.92  | 6.08  | 92.26  | 85.75     |

| s38584  | 34797 | 98.77  | 1.23  | 95.35  | 82.55     |

left. This corresponds to a reduction of the remaining faults down to 27%.

For circuits s820 and s1423 a careful selection of the random scheme even makes the deterministic test superfluous. Finally, it should be noted that for the larger circuits already a small relative reduction means a considerable number of faults which are additionally covered by the random test and need not be considered during the deterministic test. For example for circuit s38417 a reduction down to 85.75% and 92.26%, respectively, means that additional 313 and 158, respectively, faults are eliminated during random test.

Table 9 shows the resulting number of test patterns required for the random pattern resistant faults and the amount of test data storage (in bits) for the best random scheme compared to a random test using an average single polynomial. This includes the storage needed for the polynomials, the initial LFSR states for the random test and the encoded deterministic test set. Since the goal of this work was to determine the impact of the random test on the test data storage, a standard ATPG tool was selected to perform the experiments [33]. For all circuits the fault efficiency is 100% after the deterministic test.

|         |                | rministic<br>atterns | Test data storage<br>(bits) |                       |  |

|---------|----------------|----------------------|-----------------------------|-----------------------|--|

| Circuit | Best<br>scheme | Average polynomial   | Best<br>scheme              | Average<br>polynomial |  |

| c2670   | 73             | 77                   | 4186                        | 4239                  |  |

| c3540   | 1              | 1                    | 59                          | 59                    |  |

| c7552   | 51             | 92                   | 6889                        | 11644                 |  |

| s420.1  | 22             | 34                   | 503                         | 776                   |  |

| s641    | 7              | 11                   | 261                         | 321                   |  |

| s713    | 7              | 11                   | 284                         | 321                   |  |

| s820    | 0              | 32                   | 95                          | 559                   |  |

| s832    | 2              | 33                   | 146                         | 575                   |  |

| s838.1  | 78             | 120                  | 3246                        | 4749                  |  |

| s953    | 5              | 50                   | 159                         | 847                   |  |

| s1196   | 7              | 20                   | 198                         | 413                   |  |

| s1238   | 7              | 21                   | 198                         | 431                   |  |

| s1423   | 0              | 5                    | 184                         | 207                   |  |

| s5378   | 22             | 31                   | 759                         | 883                   |  |

| s9234   | 216            | 237                  | 11766                       | 12772                 |  |

| s13207  | 171            | 179                  | 10796                       | 11101                 |  |

| s15850  | 237            | 246                  | 11826                       | 12267                 |  |

| s38417  | 658            | 795                  | 71491                       | 85813                 |  |

| s38584  | 187            | 195                  | 11529                       | 12077                 |  |

*Table 9.* Number of deterministic patterns and storage requirements for the complete test data (in bits).

The results show that an optimized random test, in fact, considerably reduces the number of deterministic patterns and the overall test data storage. This is particularly true for the circuits known as random pattern resistant. For example, for circuit c7552 the number of deterministic patterns is reduced from 92 to 51 and the reduction in test data storage is about 5K. For circuit s38417 the best scheme eliminates 137 deterministic patterns, which leads to a reduction in test data storage of more than 14K. As shown in Table 10 already with standard ATPG the proposed technique requires less test data storage than an approach based on storing a compact test set (cf. [9, 20–22]).

It can be expected, that the test data storage for the presented approach could be reduced even further, if an ATPG tool specially tailored for the encoding scheme were used as described in [24].

## 7. Conclusion

A scheme for generating mixed-mode test programs for embedded processors has been presented. The test

|         |                | ministic<br>terns   | Test data storage<br>(bits) |                     |  |

|---------|----------------|---------------------|-----------------------------|---------------------|--|

| Circuit | Best<br>scheme | Compact<br>test set | Best<br>scheme              | Compact<br>test set |  |

| c2670   | 73             | 51                  | 4186                        | 8007                |  |

| c3540   | 1              | 97                  | 59                          | 4850                |  |

| c7552   | 51             | 84                  | 6889                        | 17304               |  |

| s420.1  | 22             | 43                  | 503                         | 1505                |  |

| s641    | 7              | 24                  | 261                         | 1296                |  |

| s713    | 7              | 23                  | 284                         | 1242                |  |

| s820    | 0              | 95                  | 95                          | 2185                |  |

| s832    | 2              | 96                  | 146                         | 2208                |  |

| s838.1  | 78             | 75                  | 3246                        | 5025                |  |

| s953    | 5              | 77                  | 159                         | 3465                |  |

| s1196   | 7              | 117                 | 198                         | 3744                |  |

| s1238   | 7              | 129                 | 198                         | 4128                |  |

| s1423   | 0              | 29                  | 184                         | 2639                |  |

| s5378   | 22             | 104                 | 759                         | 22256               |  |

| s9234   | 216            | 116                 | 11766                       | 28652               |  |

| s13207  | 171            | 235                 | 10796                       | 164500              |  |

| s15850  | 237            | 113                 | 11826                       | 69043               |  |

| s38417  | 658            | 91                  | 71491                       | 151424              |  |

| s38584  | 187            | 141                 | 11529                       | 206424              |  |

program uses both new, highly efficient random test schemes and a new software-based encoding of deterministic patterns.

It has been shown that the careful selection of primitive polynomials for LFSR-based random pattern generation has a strong impact on the number of undetected faults, and a multiple-polynomial random pattern scheme provides significantly better results in many cases. The quality of the random scheme has the main impact on the overall size of a mixed-mode test program. As an example, for the processor INTEL 80960CA test programs were generated, and for all the benchmark circuits a complete coverage of all non-redundant faults was obtained.

## Acknowledgment

This work was supported by the DFG grant "Test und Synthese schneller eingebetteter Systeme" (Wu 245/1-1).

*Table 10.* Amount of test data storage for the proposed approach and for storing a compact test set.

## References

- A. Flint, "Multichip Module Self-Test Provides Means to Test at Speed," *EE-Evaluation Engineering*, pp. 46–55, Sept. 1995.

- S.B. Akers and W. Jansz, "Test Set Embedding in a Built-in Self-Test Environment," *Proc. IEEE Int. Test Conf.*, Washington, DC, 1989, pp. 257–263.

- P. Bardell, W.H. McAnney, and J. Savir, *Built-in Test for VLSI*, Wiley-Interscience, New York, 1987.

- Z. Barzilai, D. Coppersmith, and A.L. Rosenberg, "Exhaustive Generation of Bit Patterns with Applications to VLSI Self-Testing," *IEEE Trans. on Comp.*, Vol. C-32, No. 2, pp. 190–194, Feb. 1983.

- F. Brglez et al., "Hardware-Based Weighted Random Pattern Generation for Boundary-Scan," *Proc. IEEE Int. Test Conf.*, Washington, DC, 1989, pp. 264–274.

- M. Chatterjee and D.K. Pradhan, "A New Pattern Biasing Technique for BIST," Proc. of VLSI Test Symp., 1995, pp. 417–425.

- C. Dufaza, H. Viallon, and C. Chevalier, "BIST Hardware Generator for Mixed Test Scheme," *Proc. Europ. Design and Test Conf.*, Paris, 1995.

- B. Koenemann, "LFSR-Coded Test Patterns for Scan Designs," *Proc. Europ. Test Conf.*, Munich, 1991, pp. 237–242.

- N.A. Touba and E.J. McCluskey, "Synthesis of Mapping Logic for Generating Transformed Pseudo-Random Patterns for BIST," *Proc. IEEE Int. Test Conf.*, Washington, DC, 1995, pp. 674–682.

- E.J. McCluskey and L.T. Wang, "Circuits for Pseudo-Exhaustive Test Pattern Generation," *Proc. IEEE Int. Test Conf.*, Washington, DC, 1986, pp. 25–37.

- H.-J. Wunderlich, "Self Test Using Unequiprobable Random Patterns," Proc. IEEE 17th Int. Symp. on Fault-Tolerant Computing, FTCS-17, Pittsburgh 1987, pp. 258–263.

- H.-J. Wunderlich, "Multiple Distributions for Biased Random Test Patterns," *Proc. IEEE Int. Test Conf.*, Washington, DC, 1988, pp. 236–244.

- S. Hellebrand, S. Tarnick, J. Rajski, and B. Courtois, "Generation of Vector Patterns Through Reseeding of Multiple-Polynomial Linear Feedback Shift Registers," *Proc. IEEE Int. Test Conf.*, Baltimore, 1992, pp. 120–129.

- S. Hellebrand, J. Rajski, S. Tarnick, S. Venkataraman, and B. Courtois, "Built-In Test for Circuits with Scan Based on Reseeding of Multiple-Polynomial Linear Feedback Shift Registers," *IEEE Trans. on Comp.*, Vol. 44, No. 2, pp. 223–233, Feb. 1995.

- N. Zacharia, J. Rajski, and J. Tyszer, "Decompression of Test Data Using Variable-Length Seed LFSRs," *Proc. 13th VLSI Test Symp.*, 1995, pp. 426–433.

- S. Gupta, J. Rajski, and J. Tyszer, "Test Pattern Generation Based On Arithmetic Operations," *Proc. Int. Conf. on Computer-Aided Design*, San Jose, CA, 1994, pp. 117–124.

- N. Mukherjee, M. Kassab, J. Rajski, and J. Tyszer, "Accumulator Built-In Self Test for High-Level Synthesis," *VLSI Test Symp.*, 1995, pp. 132–139.

- A.P. Stroele, "A Self-Test Approach Using Accumulators as Test Pattern Generators," *Proc. Int. Symp. on Circuits and Systems*, 1995, pp. 2120–2123.

- I. Voyiatzis, A. Paschalis, D. Nikolos, and C. Halatsis, "Accumulator-Based BIST Approach for Stuck-Open and Delay Fault

Testing," Proc. Europ. Design and Test Conf., Paris, 1995, pp. 431-435.

- H. Higuchi, N. Ishiura, and S. Yajima, "Compaction of Test Sets Based on Symbolic Fault Simulation," *Synthesis and Simulation Meeting and Int. Interchange*, 1992, pp. 253–262.

- S. Kajihara, I. Pomeranz, K. Kinoshita, and S.M. Reddy, "Cost-Effective Generation of Minimal Test Sets for Stuck-at Faults in Combinational Logic Circuits," *Proc. 30th ACM/IEEE Design Automation Conf.*, 1993, pp. 102–106.

- L.N. Reddy, I. Pomeranz, and S.M. Reddy, "ROTCO: A Reverse Order Test Compaction Technique," *Proc. IEEE EURO-ASIC Conf.*, Sept. 1992, pp. 189–194.

- G. Tromp, "Minimal Test Sets for Combinational Circuits," *Proc. IEEE Int. Test Conf.*, Nashville, TN, 1991, pp. 204–209.

- S. Hellebrand, B. Reeb, S. Tarnick, and H.-J. Wunderlich, "Pattern Generation for a Deterministic BIST Scheme," *Proc. IEEE/ACM Int. Conf. on CAD-95*, San Jose, CA, Nov. 1995, pp. 88–94.

- S. Hellebrand, H.-J. Wunderlich, and A. Herwig, "Mixed-Mode BIST Using Embedded Processors," *Proc. IEEE Int. Test Conf.*, Washington, DC, 1996, pp. 195–204.

- S.W. Golomb, Shift Register Sequences, Holden-Day, San Francisco, 1967.

- E.B. Eichelberger and E. Lindbloom, "Random-Pattern Coverage Enhancement and Diagnosis for LSSD Logic Self-Test," *IBM Journal or Research and Development*, Vol. 27, No. 3, May 1983.

- P.D. Hortensius, R.D. McLeod, W. Pries, D.M. Miller, and H.C. Card, "Cellular Automata-Based Pseudorandom Number Generators for Built-In Self-Test," *IEEE Trans. on CAD*, Vol. 8, No. 8, pp. 842–859, Aug. 1989.

- B. Koenemann, J. Mucha, and G. Zwiehoff, "Built-In Logic Block Observation Techniques," *Proc. Test Conf.*, Cherry Hill, NJ, 1979, pp. 37–41.

- F. Brglez and H. Fujiwara, "A Neutral Netlist of 10 Combinational Benchmark Designs and a Special Translator in Fortran," *IEEE Int. Symp. on Circuits and Systems*, Kyoto, 1985.

- F. Brglez, D. Bryan, and K. Kozminski, "Combinational Profiles of Sequential Benchmark Circuits," *Proc. IEEE Int. Symp. on Circuits and Systems*, 1989, pp. 1929–1934.

- J. Savir and W.H. McAnney, "A Multiple Seed Linear Feedback Shift Register," *IEEE Trans. on Comp.*, Vol. 41, No. 2, pp. 250– 252, Feb. 1992.

- M. Schulz and E. Auth, "Advanced Automatic Test Generation and Redundancy Identification Techinques," *Proc. 18th Int. Symp. on Fault-Tolerant Computing*, Tokyo, 1988, pp. 30–35.

Sybille Hellebrand received her diploma degree in Mathematics from the University of Regensburg, Germany, in 1986. In 1986 she joined the Institute of Computer Design and Fault Tolerance, University of Karlsruhe, where she received the Ph.D. degree in 1991. Then she was a postdoctoral fellow at the TIMA/IMAG-Computer Architecture Group, Grenoble, France. From 1992 to 1996 she worked as an assistant professor at the University of Siegen, Germany. After a sabbatical stay at Mentor Graphics Corp., Wilsonville, Oregon, she joined the Division of Computer Architecture at the University of Stuttgart, Germany, in 1997. Her main research interests include BIST for high quality applications and synthesis of testable systems. Hans-Joachim Wunderlich received the Dipl.-Math. degree in Mathematics from the University of Freiburg, Germany, in 1981, and the Dr. rer. nat. (Ph.D.) degree in Computer Science from the University of Karlsruhe in 1986. In 1983 he joined the Institute of Computer Design and Fault Tolerance, University of Karlsruhe, where he was the head of a research group on automation of circuit design and test from 1986 to 1991. From 1991 to 1996 he was a full professor for computer science at the University of Siegen. He changed to the University of Stuttgart in 1996 where he currently holds the position of a full professor and is head of the Division of Computer Architecture. His main interests are in the fields of self-testable systems, on-line test, and fault tolerance.

Andre Hertwig received his diploma degree in Computer Science from the University of Siegen, Germany, in 1995, where he joined the Institute of Computer Structures. Since 1996 he has been working at the Division of Computer Architecture, University of Stuttgart, Germany. His research interests include synthesis of testable systems and low power design.