# ERFASSUNG UND MODELLIERUNG KOMPLEXER FUNKTIONSFEHLER IN MIKROELEKTRONIK-BAUELEMENTEN

Olaf Stern, Hans-Joachim Wunderlich, Fachbereich für Elektrotechnik und Informatik, Universität-GHS-Siegen\*

Kurzfassung: Es wird ein Verfahren vorgestellt, das für die Grundzellen einer Zellbibliothek layoutabhängig die möglichen Fehlfunktionen bestimmt, die durch Fertigungsfehler verursacht werden können. Eingabe für das Verfahren sind neben dem Layout einer Zelle die Prozeßparameter und die Defektverteilungen, Ausgabe sind die realistischen Fehlfunktionen mit ihren Auftrittswahrscheinlichkeiten. Damit können Testerzeugung und Testablauf beschleunigt, schwer testbare Fehler bestimmt und ihre Ursachen lokalisiert und beseitigt werden.

Schlagworte: Fertigungstest, Fehlermodellierung, Ausbeute, Testerzeugung

## 1 Einleitung

Bei der Fertigung von Mikroelektronik-Bauelementen treten mit statistischer Gesetzmäßigkeit auch defekte Schaltungen auf. Der Ausfall von Bauelementen wird dabei durch globale Defekte (z.B. Maskenverschiebungen, Prozeßabweichungen) sowie durch lokale Defekte (z.B. Verunreinigungen der Maske, der Chemikalien oder der Waferoberfläche), sogenannte Punktdefekte, verursacht. Letztere können zu lokal sehr begrenzten Funktionsveränderungen und zu schwer erkennbaren Fehlern führen, die im Test erfaßt werden müssen, um eine ausreichende Qualität der ausgelieferten Schaltungen zu gewährleisten.

Aus Aufwandsgründen beschränkt man sich bei der Testerzeugung und beim Testablauf auf eine Teilmenge der durch die Funktionsveränderungen hervorgerufenen Fehlfunktionen. Diese werden in sogenannten Fehlermodellen dargestellt, die das fehlerhafte Verhalten auf unterschiedlichen Abstraktionsebenen modellieren. Der Nutzen des heute zumeist verwendeten Haftfehlermodells ist begrenzt, da es nur einen geringen Bezug zum Layout der Schaltung hat und komplexes Fehlverhalten nicht ausreichend modelliert [1,2,3,4,5]. Es werden tatsächlich vorkommende Fehler nicht erfaßt, zugleich werden Fehler modelliert, die in der Realität nicht vorkommen können, und eine Gewichtung der Fehler nach ihrer Auftrittswahrscheinlichkeit ist nicht möglich. Der Hersteller wird jedoch die höchstmögliche Qualität für seine ausgelieferten Schaltungen anstreben ("zero defect"). Entsprechend muß der Test alle Fehler des Fehlermodells erfassen, das seinerseits alle realistischen Fehlfunktionen enthalten soll. Die Darstellung, Erzeugung und Test aller realistischen Fehlfunktionen ist für umfangreiche Schaltungen nur in Einzelfällen, für Grundzellen dagegen auch allgemein möglich.

Im vorliegenden Beitrag wird ein Verfahren vorgestellt, mit dem analytisch sehr effizient das realistische Fehlverhalten von Zellen zu bestimmen ist. Es berücksichtigt bei der Analyse das reale Layout der Schaltung sowie statistische Daten über die in dem verwendeten Prozeß auftretenden Defekte. Die extrahierten Fehlfunktionen werden als Topologie- oder Parameterände-

<sup>\*</sup> Die Arbeit wurde in Teilen von der DFG gefördert und am Institut für Rechnerentwurf und Fehlertoleranz der Universität Karlsruhe durchgeführt.

rungen einer elektrischen Netzliste beschrieben. Da auch bereits bei kleinen Schaltungen die Anzahl der Fehlermöglichkeiten sehr groß ist, findet eine Gewichtung der Fehler nach ihrer Auftrittswahrscheinlichkeit statt, um eine effiziente Erzeugung und Verwendung beim Test zu ermöglichen.

Im folgenden Abschnitt werden die betrachteten Defekte modelliert und klassifiziert, im dritten Abschnitt wird gezeigt, wie die Defekte nach ihrer Auftrittswahrscheinlichkeit gewichtet extrahiert werden können, und anschließend werden die Defekte mit dem erwarteten Fehlverhalten der Schaltung in Beziehung gesetzt. Im letzten Abschnitt werden einige Anwendungen des Verfahrens diskutiert.

#### 2 Modellierung und Klassifizierung von Defekten

Als Defekt wird jegliche physikalische Veränderung der Schaltungsstruktur einer integrierten Schaltung bezeichnet. Häufige Defektursachen sind Verunreinigungen der Geräte, der verwendeten Chemikalien, der Luft selber oder Kristallfehler auf dem Wafer, die alle zu einem fehlerhaften Verhalten der Schaltung führen können.

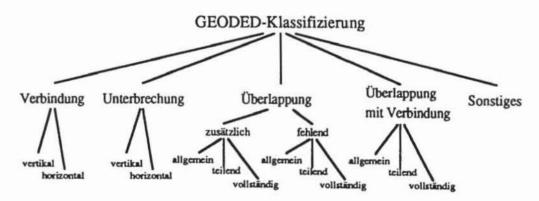

Unterschiedliche Defekte können auf der Layoutebene durch ein zuviel oder zuwenig an Material auf mindestens einer Layoutschicht modelliert werden [6]. Komplexere Defektarten können durch gleichzeitiges zuviel und zuwenig an Material auf einer oder mehreren Schichten dargestellt werden. Um die Vielzahl der elementaren geometrischen Veränderungen (Verbindung, Unterbrechung, Überlappung) durch mögliche Defekte handhaben zu können, wurde ein Klassifikationsschema entwickelt, das sowohl die topologischen Eigenschaften des Layouts als auch die Auswirkungen auf der elektrische Ebene berücksichtigt [7]. Abbildung 1 zeigt die entwickelte GEODED-Klassifizierung (GEOme-trische DEformationen beim Defekteinbau).

Abb. 1: Klassifizierung von Defekten auf der Layoutebene

Der Modellierung der Defekte liegt keine einheitliche Form zugrunde, wie andere Ansätze sie voraussetzen (quadratische [8,9,10], achteckige [11] sowie kreisförmige [12,13] Form).

#### 3 Defektanalyse

Ein elementarer Ansatz der realistischen Fehlermodellierung ist, die Defekte einzeln in das Layout der Schaltung einzubauen und die jeweiligen Auswirkungen zu extrahieren [14]. Die Auswirkungen können z.B. durch einen Vergleich der extrahierten elektrischen Netzlisten (oder der Simulationsergebnisse) der defektfreien und der defektbehafteten Schaltung erfolgen.

Bekannte Verfahren, wie die induktive Fehleranalyse [15,16,17], "bauen" die Defekte vollständig [8,9] oder probabilistisch [11,10] über ein Raster in das Schaltungslayout ein. Anschließend wird die Auswirkung durch lokale Extraktion der defektbehafteten Schaltung bestimmt. Ungünstig ist bei dieser Vorgehensweise die große Anzahl von einzelnen Analysen, die zum größten Teil (nach Walker > 94% [11]) überflüssig durchgeführt werden. Vermieden werden kann dies durch einen Ansatz, der analytisch vorgeht [12,13]. Die derzeit entwickelten analytischen Verfahren sind jedoch sehr eingeschränkt (Auswirkungen von Defekten werden nur auf Kurzschlüsse zwischen Leitungen untersucht) und ungenau (Berechnung der Häufigkeit der Fehlfunktionen, Modellierung der Defektform).

Das hier vorgestellte Verfahren basiert auf dem analytischen Ansatz, bei dem die Häufigkeit einer Fehlfunktion über die "kritische Fläche" ("critical area") abhängig von der Defektgrößenverteilung berechnet wird. Die kritische Fläche ist die Fläche, auf der ein Defekt zu einer topologischen Veränderung führt. Kritische Flächen wurden für die Ausbeutevorhersage eingeführt [18,19,20]. Mit ihrer Hilfe ist es möglich, die Anzahl der Analysen so gering wie möglich zu halten und zugleich die einzelne Analyse hinreichend genau und effizient durchzuführen.

Die Reduzierung der Anzahl der einzelnen Analysen wird durch die erwähnte Defektklassenbildung, einer Zerlegung des Layout in elementare Flächen (EF) und einer Gewichtung der Analysereihenfolge erreicht.

Als EF werden Teile eines Layouts bezeichnet, auf der Defekte aus derselben Defektklasse zu gleichen topologischen Veränderungen gemäß der aufgestellten Klassifizierung und somit auch zu einem gleichen Fehlverhalten auf höheren Abstraktionsebenen führen. Entsprechend braucht innerhalb einer EF nur jeweils ein Defekt repräsentativ für eine Defektklasse analysiert werden. Die EF müssen eine reguläre Form (hier Rechtecke) aufweisen, um eine effiziente Analyse zu ermöglichen.

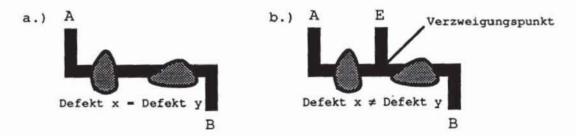

Abb. 2: Äquivalente (a) und nicht äquivalente (b) Auswirkungen von Defekten

Die Zerlegung eines Layouts in EF soll an Abbildung 2 verdeutlicht werden. Die Defekte x und y haben einmal (a) die gleichen Auswirkungen - die Unterbrechung der Verbindung von A nach B -, im anderen Fall (b) können ihre Auswirkungen dagegen unterschiedlich sein. Hier wird bereits sichtbar, daß Verzweigungspunkte gefunden und gesondert bearbeitet werden müssen. In Abbildung 5a wird die Zerlegung eines Inverters in EF dargestellt.

## 3.1 Analyse elementarer Flächen

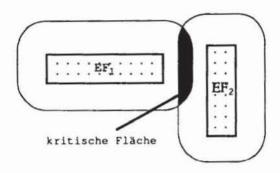

Für jede der klassifizierten topologischen Veränderungen wurde ein analytisches Verfahren entwickelt, das die kritische Fläche abhängig von der Defektart und der Defektgröße berechnet. Abbildung 3 zeigt dies für die horizontale Verbindung zweier elementarer Flächen  $\mathrm{EF}_1$  und  $\mathrm{EF}_2$  und einer festen Defektgröße.

Abb. 3: Kritisches Gebiet für die horizontale Verbindung zweier EF

Während für die Berechnung der kritischen Fläche für die horizontale Verbindung auf bekannte Verfahren aufgesetzt werden konnte, mußten für die übrigen GEODED-Klassen neue Verfahren entwickelt werden.

# 3.2 Integrierte Defektanalyse

Den prinzipiellen Ablauf der Fehlermodellierung, der sich in fünf Schritte unterteilt, zeigt Abbildung 4.

- Zunächst wird das Layout aufbereitet und in EF zerlegt. Die Zerlegung liefert nach Layerkombinationen getrennte und nach Flächeninhalten sortierte Listen EF. Der hierzu verwendete Algorithmus erzeugt unter den gegebenen Randbedingungen eine minimale Anzahl von EF (vergl. Abb. 5a).

- Für das zerlegte Layout wird durch ein erweitertes Extraktionsverfahren eine modifizierte elektrische Netzliste erzeugt. In ihr werden Verzweigungspunkte als zusätzliche Knoten mit ihren parasitären Parametern dargestellt, um die tatsächliche Leitungsführung des Layouts nachzubilden. Außerdem werden elementare Flächen den Elementen der Transistornetzliste zugeordnet.

- Anschließend wird eine Analysereihenfolge abhängig vom Flächeninhalt der EF und der Defektverteilung bestimmt. Sie steuert die folgende Defektanalyse, indem sie angibt, welche Kombination aus EF und Defektklasse als nächstes zu analysieren ist. Dies gewährleistet, daß die Defektanalyse in der Reihenfolge fallender Auftrittswahrscheinlichkeiten der Fehlfunktionen durchgeführt wird.

Abb. 4: Ablauf der integrierten Defektanalyse

- Aufgabe der folgenden Defektanalyse ist es, für die gegebene Kombination aus EF und Defektklasse die Fehlfunktion auf elektrischer Ebene sowie ihre Auftrittswahrscheinlichkeit zu bestimmen. Letztere wird abhängig von der Defektdichte durch das im Abschnitt 3.1 skizzierte Verfahren berechnet. Die einzelnen Defektanalysen werden solange fortgeführt, bis eine vorgegebene Defekterfassung erreicht ist. - Abschließend wird die Vielzahl der ermittelten Fehlfunktionen durch Zusammenfassen äquivalenter und Entfernen irrelevanter Fehlfunktionen reduziert. Die verbleibenden Fehlfunktionen werden in Form einer nach Auftrittswahrscheinlichkeit sortierten Fehlerliste ausgegeben.

## 4 Abbildung von Defekten auf die Netzlistenebene

Die extrahierten Fehlfunktionen werden auf der elektrischen Ebene als Veränderungen der erweiterten Transistornetzliste modelliert. Dabei wird grundsätzlich zwischen topologischen Veränderungen und Parameteränderungen unterschieden. Topologische Veränderungen sind Veränderungen, die sich in der Struktur der Netzliste bemerkbar machen, d.h. das Fehlen sowie das zusätzlichen Vorhandensein von Elementen oder Verbindungen. Parameteränderungen sind z.B. Widerstands- oder Kapazitätsveränderungen von internen Knoten, Leitungen oder Bauelementen.

Jeder Defektklasse kann eindeutig ein Fehler auf der elektrischen Ebene zugeordnet werden. Die durch einen Defekt betroffenen elementaren Flächen lassen sich Elementen der elektrischen Netzliste zuordnen, woraus sich die Fehlfunktion ableiten läßt.

### 5 Ergebnisse und Anwendung

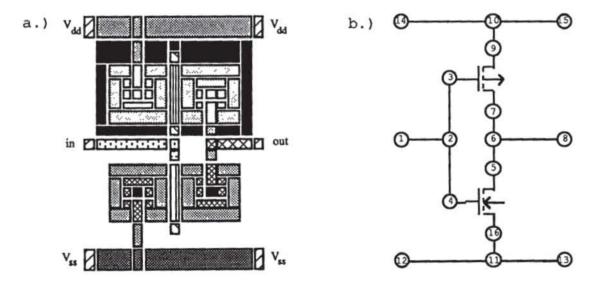

Abbildung 5 zeigt das zerlegte Layout eines Inverters in EF sowie die extrahierte erweiterte Netzliste (ohne Parameter). Mittels des vorgestellten Verfahren wurden für die Schaltung über 300 einzelne Strukturveränderungen extrahiert. Nach geeigneter Zusammenfassung ergeben sich die in Tabelle 1 aufgeführten Fehlfunktionen mit zugehöriger Wahrscheinlichkeit P  $(P>10^{-8})$ .

Abb. 5: Layout (a) und erweiterte Netzlistendarstellung (b) eines Inverters

Bereits bei einer so einfachen Teilschaltung können Defekte Fehlfunktionen bewirken, die sich nicht sicher durch das Haftfehlermodell erfassen lassen. Diese sind z.B. ständig leitender Transistor (Kurzschluß Substrat nach 3/4) oder veränderte Schwellspannung eines Transistors (Parameteränderung).

Durch die genauere, layoutabhängige Fehlermodellierung kann das Verfahren maßgeblich zur Qualitätssicherung beitragen und sogenanntes "high quality

testing" ermöglichen. Die Erzeugung von gewichteten Fehlfunktionen ermöglicht eine effizientere Testmustererzeugung sowie einen schnelleren Testablauf. Des Verfahren ermöglicht es, u.a. schwer testbare Fehlfunktionen im Bezug zum realen Layout zu bestimmen, die Ursachen im Layout zu lokalisieren und gegebenfalls durch ein testfreundlicheres Layout zu ersetzen.

| Kurzschluß: |          |          | Unterbrechung: |    |          |          |    |          |

|-------------|----------|----------|----------------|----|----------|----------|----|----------|

| von         | on nach  | P        | zwischen       |    | P        | zwischen |    | P        |

|             |          |          | 1              | 2  | 1,3.10-7 | 9        | 10 | 3.5-10-8 |

| 4           | Subtrat  | 2,4.10-6 | 6              | 8  | 9,0.10-8 | 11       | 16 | 3,1.10-8 |

| 3           | Subtrat  | 2,4.10-6 | 11             | 13 | 6,4.10-8 | 7        | 9  | 2,4.10-8 |

| 6,13        | 14,10,15 | 8,7.10-9 | 10             | 15 | 6,4.10-8 | 1        | 2  | 2,2.10-8 |

| 6,13        | 11,12,13 | 8,7.10-9 | 5              | 6  | 5,9-10-8 | 2        | 4  | 2,2.10-8 |

|             |          |          | 6              | 7  | 5,6.10-8 | 12       | 11 | 1,8.10-8 |

Tabelle 1: Gewichtete Fehlfunktionen des Inverter aus Abbildung 5

#### Literatur

- [1] J. Galiay, Y. Crouzet, M. Vergniault: Physical Versus Logical Models MOS LSI Circuits: Impact On Their Testability, IEEE Trans. on Computers, 1980.

- Wojciech Maly: Realistic Fault Modeling for VLSI Testing, IEEE DAC-24, Miami Beach 1987.

- [3] Peter C. Maxwell, Hans-Joachim Wunderlich: The Effectiveness of Different Test Sets for PLAs, 1st EDAC, Glasgow 1990.

- [4] Peter C. Maxwell, Robert C. Aitken: The Effect of Different Test Sets on Quality Level Prediction, IEEE IC Workshop, Mai 1991.

- [5] Tom Story, Wojciech Maly, John Andrews, Myron Miske: Comparing Stuck Fault and Current Testing via CMOS Chip Test, IEEE ETC, München 1991.

- [6] Hans-Joachim Wunderlich: Hochintegrierte Schaltungen: Prüfgerechter Entwurf und Test, Springer-Verlag, Berlin 1991.

- Gerald Spiegel: Defektanalyse für die Repräsentation realistischer Fehlfunktionen in hochintegrierten Schaltungen, Diplomarbeit, Institut für Rechnerentwurf und Fehlertoleranz, Universität Karlsruhe, November 1991.

- [8] F. Joel Ferguson, John P. Shen: A CMOS Fault Extractor for Inductive Fault Analysis, IEEE Trans. on CAD, Vol. 7, No. 11, November 1988.

- R.J. Evans, W.R. Moore: Layout Based Testing of CMOS Logic, Department of Engineering Science, University of Oxford, Dezember 1989.

- [10] Joel Ferguson, John P. Shen: Extraction and Simulation of Realistic CMOS Faults using Inductive Fault Analysis, IEEE ITC-88, 1988.

- [11] Duncan Moore Henry Walker: Yield Simulation for Integrated Circuits, Carnegie Mellon University, Kluwer Academic Publishers, 1987.

- [12] Phil Nigh, Wojciech Maly: Layout-Driven Test Generation, ICCAD 89, Santa Clara California 1989.

- [13] Marcel Jacomet: FANTASTIC: Toward a Powerful Fault Analysis and Test Pattern Generator for Integrated Circuits, IEEE ITC-89, 1989.

- Heike Rehme, Michael Wittke: Automatische Fehlermodellierung aufgrund der Layoutbeschreibung von MOS-Schaltungen, Diplomarbeit, Institut für Rechnerentwurf und Fehlertoleranz, Universität Karlsruhe, Oktober 1987.

- [15] W. Maly, F.J. Ferguson, J.P. Shen: Systematic Characterisation of Physical Defects

- for Fault Analysis of MOS IC Cells, IEEE ITC-84, pp. 390-399, 1984. [16] F.Joel Ferguson, John P. Shen, W. Maly: Inductive Fault Analysis of nMOS and CMOS Integratet Circuits, Departement of Electrical and Computer Engineering, Carnegie-Mellon University, Pittsburg August 1985.

- [17] Joel Ferguson: Inductive Fault Analysis of CMOS Circuits, Carnegie Mellon University, Pittsburgh November 1986.

- [18] C.H. Stapper: Modeling of defects in integrated circuits photolithographic patterns, IBM Journal of Reserch and Devolopment, Vol. 28, Juli 1984.

- [19] A.V. Ferris-Prabhu: Computation of the Critical Area in Semiconductor Yield Theory, IEEE Proc. Conference on Eletronic Design Automation, Pub. 232, 1984.

- [20] A.V. Ferris-Prabhu: Modeling the Critical Area in Yield Forecasts, IEEE Journal of Solid-State Circuits, Vol. sc-20, No. 4, August 1985.